# MARATHA MANDAL ENGINEERING COLLEGE

(R.S.No.104, Halbhavi, Post: New Vantmuri Belagavi 591113)

# A RESOURCE MATERIAL OF ANALOG CIRCUITS

MULTILINGUAL EDITION - ENGLISH, KANNADA, MARATHI

FOR UNDERGRADUATE B. E / B. TECH STUDENTS

COMPILED BY

PROF. MANI.C & PROF. SANDHYA BEVOOR

Department Of Electronics & Communication Engineering

#### FOR INTERNAL CIRCULATION ONLY

# Tresident's Message

Smt. Rajshree Nagraju President MM Group

It gives me an immense pleasure to acknowledge the contribution made by the faculties of Maratha Mandal Engineering College, Belagavi in introducing the resource material for the student community in all the three languages - English, Marathi and Kannada. This content will be useful for rural background students and vernacular medium students. This is a unique reading material first of its kind as per the guidelines of National Education policy (NEP) to be introduced in Engineering education for betterment of students in teaching - learning process.

# Foreward

I am extremely happy and take this opportunity to highlight that **Prof. Sandhya Bevoor** and **Prof. Maní C.** of Maratha Mandal Engineering college, Belagaví has compiled a Multilingual text book on Analog Circuits which will be helpful to 2<sup>nd</sup> year undergraduate B.E / B.Tech Students of Electrical and Electronics branches of engineering.

The faculties from the department of Electronics and Communication engineering have been dedicated in teaching this subject and I am sure that this book which is written in English, Kannada and Marathi will be an great asset for student community.

I would recommend this textbook not only for students but also to everyone who want to upgrade and advance their knowledge in the field of analog Electronics.

**Dr. D. G. Kulkarni**Ph.d, M.Tech, MBA, PGDM,

PGTD, MISTE, MISTD, MISCM(USA)

Principal

Maratha Mandal Engineering

College, Belagavi

# Preface

This book is a product of my dedicated teaching experience of 15 years for the subject "Analog Electronics". The concepts of the subject are explained in a systematic and logical manner and written and explained in English, Kannada and Marathi for the student's community in a user friendly manner. It is Simple and some relevant problems are solved for better understanding in designing the application circuits.

The books introduce concepts of biasing, amplification, feedback circuits using BJTs and Mosfets along with application circuits using op-amps at undergraduate level for Electrical and electronics students.

Despite efforts taken to introduce the textbook, I would also apologise for any type errors introduced and all levels of corrections will be implemented in the next edition.

# **ACKNOWLEDGEMENT**

My síncere gratítude to Smt. Rajshree Nagaraju, Presídent, Maratha Mandal Group of Institutions, Belagaví, who inspired me to take up and successfully complete this task.

A special word of thanks to **Dr. S. VidyashankarJi**, honourable vice-chancellor, Visveswaraiah Technological University (VTU), Belagavi, **Dr. B. E. Rangaswamy**, registrar V.T.U, **Dr. T. N. Sreenivasa**, Registrar (Evaluation), V.T.U who are always an infinite source of encouragement in all my endeavours.

I gratefully and thankfully acknowledge all the encouragement from **Dr. D. G. Kulkarni,** Principal, Maratha Mandal Engineering College, Belagavi in providing guidance and providing support, facilities and resources in drafting this material.

I sincerely thank my beloved Head of Electronics and communication engineering department, **Prof. Vaibhav Kakade**, who encouraged me to take up this assignment. His support and invaluable suggestions at each and every stage of drafting this material are unforgettable. I hope without his support and encouragement, this book would hardly be in its present form.

I must thank all my colleagues in the department of Electronics and Communication, M.M.E.C, Belagavi, for all their suggestion towards improving the material presented.

I must acknowledge all the encouragement and timely support from my family members without them it wouldn't have been possible for completion of this task.

# **CONTENTS**

#### MODULE 1

# 1.1. BJT Biasing: Biasing in BJT Amplifier Circuits

- 1.11 Introduction

- 1.12 The Classical Discrete Circuit Bias Arrangement

- 1.13 Biasing using Collector to Base Feedback bias

### 1.2. Small Signal Operations and Models

- 1.21 Collector current and Transconductance

- 1.22 Base Current and Base input resistance

- 1.23 Emitter Current and Emitter input resistance

- 1.24 Voltage gain

- 1.25 Separating the Signal and DC quantities

- 1.26 The Hybrid  $\pi$  Model

- 1.27 The T Model

#### 1.3. MOSFETS: Biasing in MOS Amplifier Circuits

- $1.31 \; Fixing \; V_{GS}$

- $1.32 \; Fixing \; V_G$

- 1.33 Drain to Gate Feedback Resistor

#### 1.4. Small Signal Operation and Modelling

- 1.41 The DC Bias Point

- 1.42 Signal Current in drain terminal

- 1.43 Voltage gain

- 1.44 Small Signal Equivalent Circuit Models

- 1.45 Transconductance

- 1.46 T Equivalent Circuit Model

#### **MODULE 2**

#### 2.1. MOSFET Amplifier Configuration

- 2.11 Basic Configurations

- 2.12 Characterizing Amplifiers

- 2.13 Common Source Amplifiers with and without Source resistance

- 2.14 Source follower

- 2.15 Comparison of MOSFET Amplifiers

#### 2.2. MOSFET Internal Capacitances and High Frequency Model

- 2.21 The Gate Capacitive effect

- 2.22 Junction Capacitances

- 2.23 High Frequency Model

# 2.3. Frequency Response of Common Source Amplifier

- 2.31 Three Frequency Bands

- 2.32 Low Frequency Response of CS Amplifier

- 2.33 High Frequency Response of CS Amplifier

#### 2.4. Oscillators

- 2.41 Phase Shift Oscillator

- 2.42 LC and Crystal Oscillators

#### MODULE 3

#### 3.1. Output Stages and Power Amplifiers

- 3.11 Introduction

- 3.12 Classification of output stages

- 3.13 Class A Output Stage

- 3.2 Class B Output Stage

- 3.3 Class AB Output stage

- 3.4 Class -C Tuned Amplifier

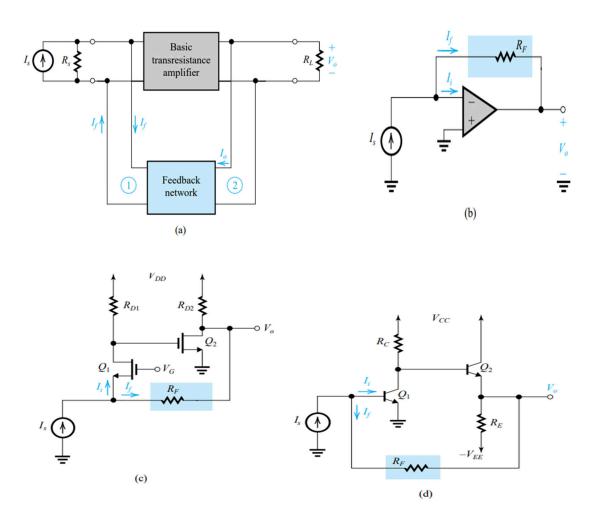

# 3.5. Feedback Amplifier

- 3.51 General feedback Structure

- 3.52 Properties of Negative Feedback

- 3.53 The Four Basic Feedback Topologies

#### **MODULE 4**

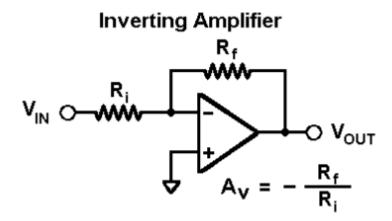

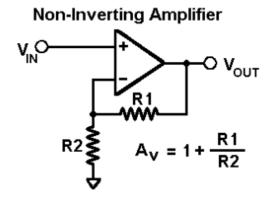

#### 4.1. Op-Amp DC and AC Amplifiers

- 4.11 Inverting

- 4.12 Non-inverting Amplifiers

- 4.13 AC characteristics

#### 4.2. Filters

- 4.2.1 First order Low Pass Butterworth Filter

- 4.2.2 First order High Pass Butterworth Filter

- 4.2.3 Band Pass Filter

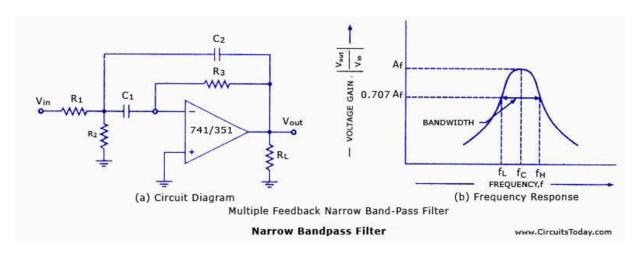

- 4.2.4 Narrow Band Pass Filter

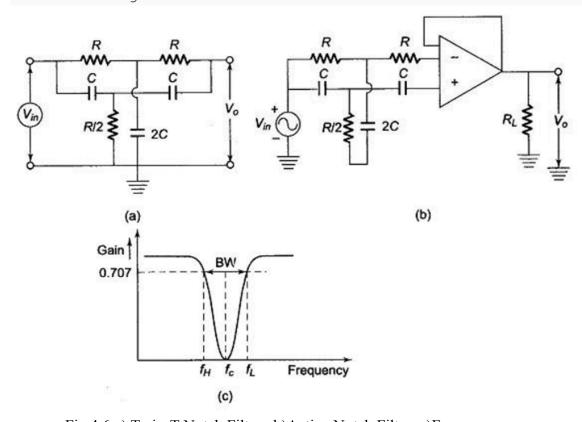

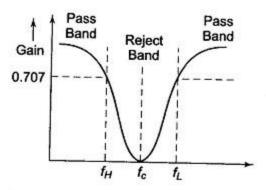

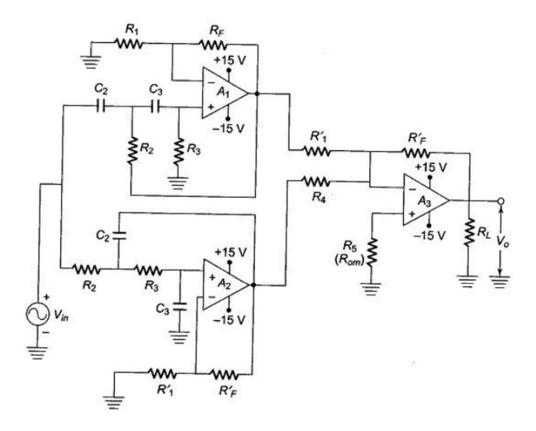

- 4.2.5 Band Reject Filter

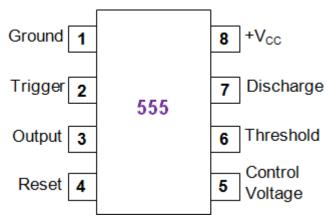

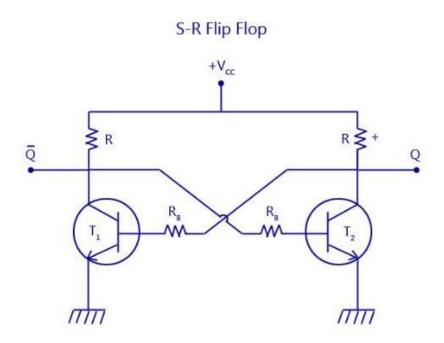

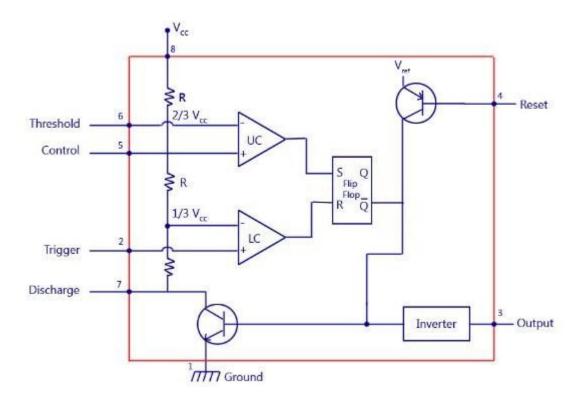

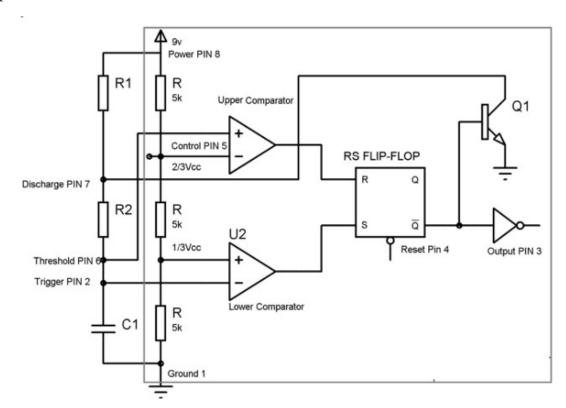

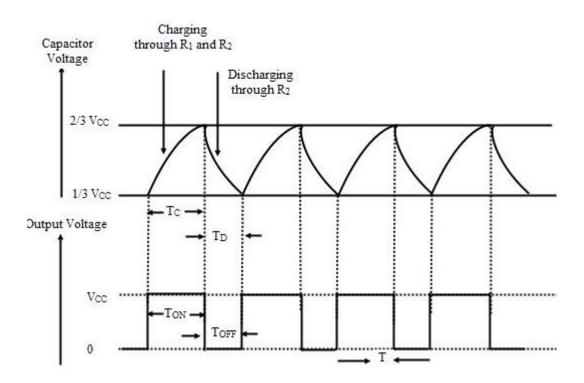

# 4.3 555 Timer and its Applications

- 4.3.1 Introduction

- 4.3.2 Important features of 555 Timer

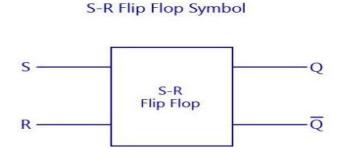

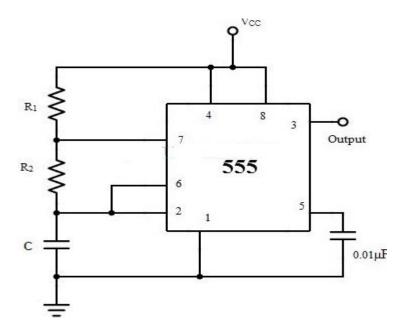

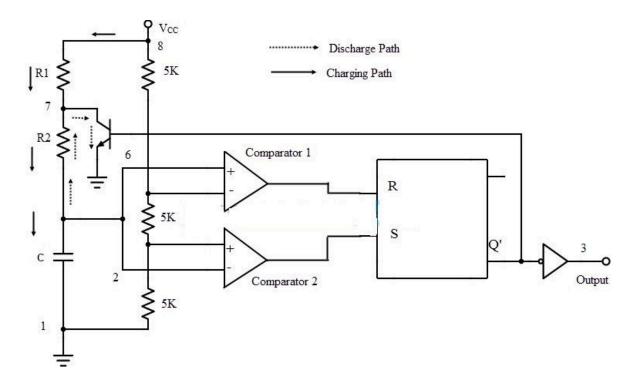

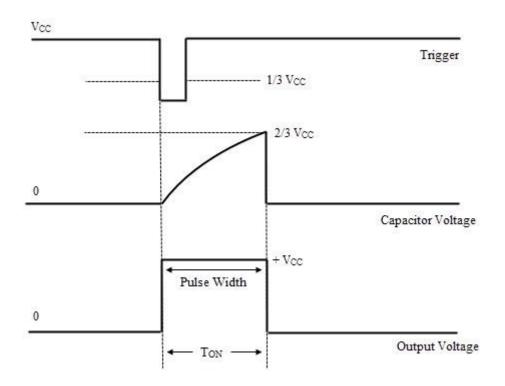

#### 4.4 Monostable Multivibrator

- 4.4.1 Operation

- 4.5. Astable Multivibrator

## **MODULE 5**

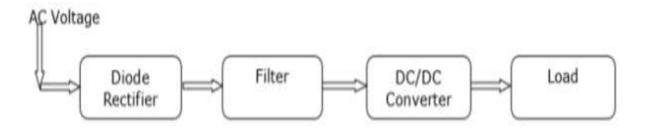

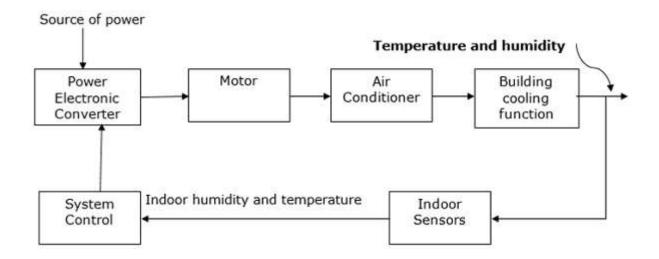

- 5.1. Introduction to Power Electronics

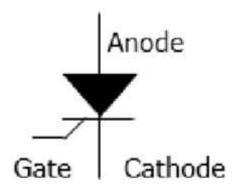

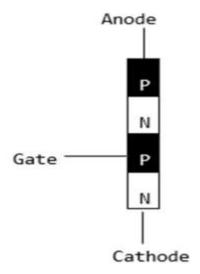

- 5.2. Thyristors

- 5.3 Turn On Methods Of SCR

- 5.4 Turn Off Methods Of SCR

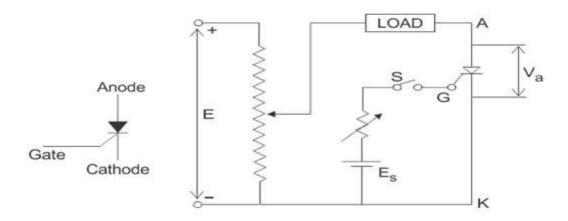

- 5.5 Resistance Firing Circuit

- 5.6.R-C Firing Circuit

- 5.7 UJT Firing Circuit

1.1 BJT Biasing: Biasing in BJT Amplifier Circuits: The Classical Discrete circuit bias (Voltage – divider Bias), Biasing using Collector to Base Feedback bias.

#### 1.11 Introduction:

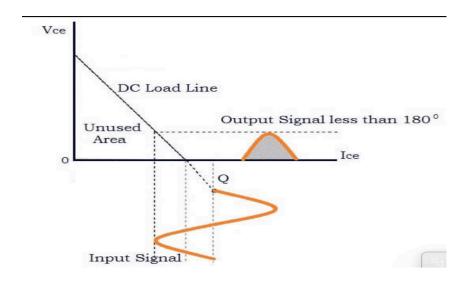

The most important application of a transistor is its use in electronic circuits as amplifier. Amplification is the process of strengthening of a weak signal i.e.; increasing its amplitude, without distortion of its waveshape. For faithful amplification, it is essential that the emitter base junction remains forward biased and the collector-base junction remains reverse biased throughout the signal period. If the junctions are not properly biased, there would be distortion at the output voltage. The transistor to work as an amplifier with faithful amplification, it is to be operated in active region (the region between cut off and saturation region). The point of intersection of d.c load line with an output characteristic at a certain level of base current is termed as operating point. It is also referred as quiescent point or Qpoint. It represents the d.c bias condition, in the absence of input signal. Its coordinates give the values of V<sub>CE</sub> and I<sub>C</sub>, corresponding to the value of I<sub>B</sub> at which the output characteristic is plotted. Different types of biasing circuits are: i) fixed current bias method or base resistor method ii) collector to base bias method iii) Self-bias or voltage divider bias method. The Voltage divider bias also called as emitter current bias configuration is most widely used of all the bias configurations. In this method of biasing a transistor, Resistors are connected across the bias battery so that they form a potential divider. The voltage drop V<sub>B</sub> remains fairly constant and provides the necessary fixed bias for the emitter base junction. Current IB flows into the base and the emitter diode is always forward biased. Once the circuit is properly biased, the weak a.c signal to be amplified is applied across the input terminals of the amplifier circuit and the output is taken across the load resistor at the output terminals of the amplifier.

ಟ್ರಾನ್ಸಿಸ್ಟರ್ನ ಅತಂ್ಯತ ಪ್ರಮುಖ ಅನ್ವಯವೆಂದರೆ ವಿದ್ಯುನ್ಮಾನ ಸರ್ಕ್ಯೂಟ್ಗಳಲ್ಲಿ ಆಂಪ್ಲಿಫಯರ್ ಆಗಿ ಅದರ ಬಳಕೆ. ಆಂಪ್ಲಿಫಿಕೇಶನ್ ಎಂಬುದು ದುರ್ಬಲ ಸಂಕೇತವನ್ನು ಬಲಪಡಿಸುವ ಪ್ರಕ್ರಿಯೆಯಾಗಿದೆ, ಅಂದರೆ ಅದರ ತರಂಗಾಂತರದ ವಿರೂಪವಿಲ್ಲದೆ ಅದರ ವೈಶಾಲ್ಯವನ್ನು ಹೆಚ್ಚಿಸುತ್ತದೆ. ವಿಶ್ವಾಸಾರ್ಹ ವರ್ಧನೆಗಾಗಿ, ಹೊರಸೂಸುವ ಬೇಸ್ ಜಂಕ್ಷನ್ ಮುಂದಕ್ಕೆ ಪಕ್ಷಪಾತದಿಂದ ಕೂಡಿರುತ್ತದೆ ಮತ್ತು ಸಂಗ್ರಾಹಕ-ಬೇಸ್ ಜಂಕ್ಷನ್ ಸಿಗ್ನಲ್ ಅವಧಿಯುದ್ದಕ್ಕೂ ರಿವರ್ಸ್ ಪಕ್ಷಪಾತದಿಂದ ಕೂಡಿರುತ್ತದೆ. ಜಂಕ್ಷನ್ಗಳು ಸರಿಯಾಗಿ ಪಕ್ಷಪಾತ ಮಾಡದಿದ್ದರೆ, ಔಟ್ಫುಟ್ ವೋಲ್ಟ್ಜ್ನಲ್ಲಿ ವಿರೂಪಗೊಳ್ಳುತ್ತದೆ. ವಿಶ್ವಾಸಾರ್ಹ

ವರ್ಧನೆಯೊಂದಿಗೆ ಆಂಪ್ಲಿಫಯರ್ ಆಗಿ ಕಾರ್ಯನಿರ್ವಹಿಸಲು ಟ್ರಾನ್ಸಿಸ್ಟರ್, ಇದು ಸಕ್ರಿಯ ಪ್ರದೇಶದಲ್ಲಿ (ಕಟ್ ಆಫ್ ಮತ್ತು ಸ್ಯಾಚುರೇಶನ್ ಪ್ರದೇಶದ ನಡುವಿನ ಪ್ರದೇಶ) ಬೇಸ್ ಪ್ರವಾಹದ ಒಂದು ನಿರ್ದಿಪ್ಟ ಮಟ್ಟದಲ್ಲಿ ಔಟ್ಫುಟ್ ಕಾರ್ಯನಿರ್ವಹಿಸಲು. ಗುಣಲಕ್ಷಣದೊಂದಿಗೆ ಡಿ. ಸಿ ಲೋಡ್ ರೇಖೆಯ ಛೇದನದ ಬಿಂದುವನ್ನು ಆಪರೇಟಿಂಗ್ ಪಾಯಿಂಟ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ. ಇದನ್ನು ಕ್ವಿಸೆಂಟ್ ಪಾಯಿಂಟ್ ಅಥವಾ ಎಕ್ಸ್-ಪಾಯಿಂಟ್ ಎಂದೂ ಕರೆಯಲಾಗುತ್ತದೆ. ಇದು ಇನ್ಫುಟ್ ಸಿಗ್ನಲ್ ಅನುಪಸ್ಥಿತಿಯಲ್ಲಿ, d. c. ಪಕ್ಷಪಾತ ಸ್ಥಿತಿಯನ್ನು ಪ್ರತಿನಿಧಿಸುತ್ತದೆ. ಇದರ ನಿರ್ದೇಶಾಂಕಗಳು IBಯ ಮೌಲ್ಯಕ್ಕೆ ಅನುಗುಣವಾದ ಡಬ್ಲ್ಯುಸಿಇ ಮತ್ತು ಐಸಿ ಮೌಲ್ಯಗಳನ್ನು ನೀಡುತ್ತವೆ, ಇದರಲ್ಲಿ ಔಟ್ಫುಟ್ ಗುಣಲಕ್ಷಣವನ್ನು ಯೋಜಿಸಲಾಗಿದೆ. ವಿವಿಧ ರೀತಿಯ ಪಕ್ಷಪಾತ ಸರ್ಕ್ಯೂಟ್ಮಳು: i) ಸ್ಥಿರ ಪ್ರಸ್ತುತ ಪಕ್ಷಪಾತ ವಿಧಾನ ಅಥವಾ ಬೇಸ್ ರೆಸಿಸ್ಟರ್ ವಿಧಾನ ii) ಬೇಸ್ ಪಕ್ಷಪಾತ ವಿಧಾನ iii) ಸ್ವಯಂ-ಬಿಯಾಸ್ ಅಥವಾ ವೋಲ್ಬೇಜ್ ವಿಭಜಕ ಪಕ್ಷಪಾತ ವಿಧಾನ. ಹೊರಸೂಸುವ ಪ್ರಸ್ತುತ ಪಕ್ಷಪಾತ ಸಂರಚನೆ ಎಂದು ಕರೆಯಲ್ಪಡುವ ಫೋಲ್ಬೇಜ್ ವಿಭಜಕ ಪಕ್ಷಪಾತವನ್ನು ಎಲ್ಲಾ ಪಕ್ಷಪಾತ ಸಂರಚನೆಗಳಲ್ಲಿ ಅತ್ಯೂತ ವ್ಯಾಪಕವಾಗಿ ಬಳಸಲಾಗುತ್ತದೆ. ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಅನ್ನು ಪಕ್ಷಪಾತ ಮಾಡುವ ಈ ವಿಧಾನದಲ್ಲಿ, ಪ್ರತಿರೋಧಕಗಳು ಪಕ್ಷಪಾತ ಬ್ಯಾಟರಿಯಾದ್ಯೂತ ಸಂಪರ್ಕ ಹೊಂದಿರುತ್ತವೆ, ಇದರಿಂದಾಗಿ ಅವುಗಳು ಸಂಭಾವ್ಯ ವಿಭಜಕವನ್ನು ರೂಪಿಸುತ್ತವೆ. ವೋಲ್ಬೇಜ್ ಡ್ರಾಪ್ ವಿಬಿ ಸಾಕಷ್ಟು ಸ್ಥಿರವಾಗಿರುತ್ತದೆ ಮತ್ತು ಹೊರಸೂಸುವ ಬೇಸ್ ಜಂಕ್ಷನ್ ಅಗತ್ಯ ಸ್ಥಿರ ಪಕ್ಷಪಾತ ಒದಗಿಸುತ್ತದೆ. ಪ್ರಸ್ತುತ ಐಬಿ ಬೇಸ್ನಲ್ಲಿ ಹರಿಯುತ್ತದೆ ಮತ್ತು ಹೊರಸೂಸುವ ಡಯೋಡ್ ಯಾವಾಗಲೂ ಮುಂದಕ್ಕೆ ಪಕ್ಷಪಾತದಿಂದ ಸರ್ಕ್ಯೂಟ್ ಸರಿಯಾಗಿ ಪಕ್ಷಪಾತ ಮಾಡಿದ ನಂತರ, ವರ್ಧಿಸಬೇಕಾದ ದುರ್ಬಲ ಎ. ಸಿ ಸಿಗ್ನಲ್ ಅನ್ನು ಆಂಪ್ಲಿಫೈಯರ್ ಸರ್ಕ್ಯೂಟ್ನ ಇನ್ಸುಟ್ ಟರ್ಮಿನಲ್ಗಳಾದಂ್ಯತ ಅನ್ನಯಿಸಲಾಗುತ್ತದೆ ಮತ್ತು ಔಟ್ಫುಟ್ ಅನ್ನು ಆಂಪ್ಲಿಫೈಯರ್ನ ಔಟ್ಫುಟ್ ಟರ್ಮಿನಲ್ಗಳಲ್ಲಿ ಲೋಡ್ ರೆಸಿಸ್ಟರ್ನಾದಂ್ಯತ ತೆಗೆದುಕೊಳ್ಳಲಾಗುತ್ತದೆ.

एक ट्रान्झिस्टर सर्वात महत्वाचे अर्ज वर्धक म्हणून इलेक्ट्रॉनिक सर्किट मध्ये त्याचा वापर आहे. आंबटपणा एक कमकुवत सिग्नल मजबूत करण्याची प्रक्रिया म्हणजे; त्याच्या waveshape विकृती न करता, त्याच्या मोठेपणा वाढत. या सर्व गोष्टींकडे लक्ष वेधले असता, हा सर्व प्रकार लक्षात येतो. जर जंक्शन योग्यरित्या पक्षपाती नसतील तर आउटपुट व्होल्टेजवर विकृती होईल. विश्वासू प्रवर्धन सह एक

प्रवर्धक म्हणून काम करण्यासाठी ट्रान्झिस्टर, तो सक्रिय प्रदेश (कट ऑफ आणि संपृक्तता प्रदेश दरम्यान प्रदेश) मध्ये ऑपरेट करणे आहे. आधार वर्तमान एक विशिष्ट पातळीवर आउटपुट वैशिष्ट्यपूर्ण डीसी लोड ओळ छेदनिबंदू बिंदू ऑपरेटिंग बिंदू म्हणतात. याला क्विसेंट पॉईंट किंवा क्यू पॉईंट असेही म्हटले जाते. हे इनपुट सिग्नल नसतानाही, d.c. पूर्वग्रह स्थिती प्रतिनिधित्व करते. त्याचे निर्देशांक VCE आणि आयसीचे मूल्य देतात, आयबीच्या मूल्याशी संबंधित ज्यावर आउटपुट वैशिष्ट्यपूर्ण प्लॉट केले जाते. विविध प्रकारच्या पक्षपाती सिर्कट आहेत: i) निश्चित वर्तमान पक्षपाती पद्धत किंवा बेस रेझिस्टर पद्धत ii) कलेक्टर टू बेस पक्षपाती पद्धत iii) स्व-पक्ष किंवा व्होल्टेज डिव्हायडर पक्षपाती पद्धत. यालाच वर्तमान पूर्वग्रह संरचना असेही म्हटले जाते, हे सर्व पूर्वग्रह संरचनांचा मोठ्या प्रमाणावर वापर केला जातो. एक ट्रान्झिस्टर पक्षपाती या पद्धतीमध्ये, विरोधक पक्षपाती बद्यरी ओलांडून जोडलेले आहेत जेणेकरून ते संभाव्य विभाजक तयार करतात. व्होल्टेज ड्रॉप VB बऱ्यापैकी स्थिर राहते आणि emitter बेस जंक्शन आवश्यक निश्चित पूर्वग्रह प्रदान करते. वर्तमान आयबी बेस मध्ये वाहते आणि emitter diode नेहमी पुढे पक्षपाती आहे. एकदा सर्किट योग्य पक्षपाती आहे, कमकुवत एसी सिग्नल प्रवर्धित करणे वर्धक सर्किट इनपुट टर्मिनल ओलांडून लागू आहे आणि आउटपुट वर्धक आउटपुट टर्मिनल येथे लोड प्रतिरोधक ओलांडून घेतले आहे

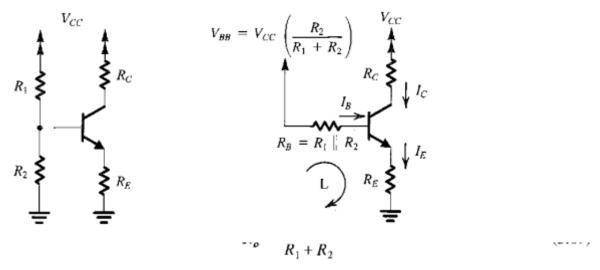

# 1.12 The Classical Discrete - Circuit Bias Arrangement:

The technique consists of supplying the base of the transistor with a fraction of the supply voltage  $V_{CC}$  through the voltage divider  $R_1$ ,  $R_2$ . In addition, a resistor  $R_E$  is connected to the emitter.

The current  $I_E$  can be determined by writing a Kirchhoff loop equation for the base-emitter-ground loop, labeled L, and substituting  $I_B = I_E/(\beta+1)$ :

$$I_E = \frac{V_{BB} - V_{BE}}{R_E + R_B/(\beta + 1)}$$

To make  $I_E$  insensitive to temperature and  $\beta$  variation,<sup>8</sup> we design the circuit to satisfy the following two constraints:

$$V_{BB} \gg V_{BE}$$

$$R_E \gg \frac{R_B}{\beta + 1}$$

For a given value of the supply voltage  $V_{CC}$ , the higher the value we use for  $V_{BB}$ , the lower will be the sum of voltages across  $R_C$  and the collector-base junction ( $V_{CB}$ ). On the other hand, we want the voltage across  $R_C$  to be large in order to obtain high voltage gain and large signal swing (before transistor cut off). We also want  $V_{CB}$  (or  $V_{CE}$ ) to be large to provide a large signal swing (before transistor saturation). As a rule of thumb, one designs for  $V_{BB}$  about (1/3)  $V_{CC}$ ,  $V_{CB}$  (or  $V_{CE}$ ) about (1/3)  $V_{CC}$ , and  $I_{CRC}$  about (1/3) $V_{CC}$ .  $I_{E}$  is made insensitive to variations in  $\beta$  and could be satisfied by selecting  $R_{B}$  small. This in turn is achieved by using low values for  $R_{1}$  and  $R_{2}$ . Lower values for  $R_{1}$  and  $R_{2}$ , however, will mean a higher current drain from the power supply, and will result in a lowering of the input resistance of the amplifier (if the input signal is coupled to the base), which is the trade-off involved in this part of the design. It should be noted that we want to make the base voltage independent of the value of  $\beta$  and determined solely by the voltage divider. This will obviously be satisfied if the current in the divider is made much larger than the base current. Typically one selects  $R_{1}$  and  $R_{2}$  such that their current is in the range of  $I_{E}$  to  $0.1I_{E}$ .

Further insight regarding the mechanism by which the bias arrangement of above figure stabilizes the dc emitter (and hence collector) current is obtained by considering the feedback action provided by  $R_E$ . Consider that for some reason the emitter current increases. The voltage drop across  $R_E$ , and hence  $V_E$  will increase correspondingly. Now, if the base voltage is determined primarily by the voltage divider  $R_1$   $R_2$ , which is the case if  $R_B$  is small, it will remain constant, and the increase in  $V_E$  will result in a corresponding decrease in  $V_{BE}$ . This in turn reduces the collector (and emitter) current, a change opposite to that originally assumed. Thus,  $R_E$  provides a negative feedback action that stabilizes the bias current.

ಸರಬರಾಜು ಪೋಲ್ಟೇಜ್ ವಿಸಿಸಿಯ ಒಂದು ನಿರ್ದಿಷ್ಟ ಮೌಲ್ಯಕ್ಕೆ, ನಾವು ವಿಬಿಬಿಗೆ ಬಳಸುವ ಹೆಚ್ಚಿನ ಮೌಲ್ಯ, ಕಡಿಮೆ ಆರ್ಸಿ ಮತ್ತು ಸಂಗ್ರಾಹಕ-ಮೂಲ ಜಂಕ್ಷನ್ ( $V_{CB}$ ) ಉದ್ದಕ್ಕೂ

ವೋಲ್ಬ್ಜ್ಜ್ಗಳ ಮೊತ್ತವಾಗಿರುತ್ತದೆ. ಮತ್ತೊಂದೆಡೆ, ಹೆಚ್ಚಿನ ವೋಲ್ಬ್ಜ್ ಲಾಭ ಮತ್ತು ದೊಡ್ಡ ಸಿಗ್ನಲ್ ಸ್ವಿಂಗ್ (ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಕಡಿತಗೊಳ್ಳುವ ಮೊದಲು) ಪಡೆಯುವ ಸಲುವಾಗಿ ಆರ್ಸಿ ಅಡ್ಡಲಾಗಿ ಫೋಲ್ಬ್ರೇಜ್ ದೊಡ್ಡದಾಗಿರಬೇಕು ಎಂದು ನಾವು ಬಯಸುತ್ತುವೆ. ದೊಡ್ಡ ಸಿಗ್ನಲ್ ಸ್ಟಿಂಗ್ (ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಸ್ಯಾಚುರೇಶನ್ ಮೊದಲು) ಒದಗಿಸಲು  $V_{CB}$  (ಅಥವಾ ವಿಸಿಇ) ದೊಡ್ಡದಾಗಿರಬೇಕು ಎಂದು ಸಹ ನಾವು ಬಯಸುತ್ತೇವೆ. ಹೆಬ್ಬೆರಳಿನ ನಿಯಮದಂತ್ರೆ  $V_{BB}$ ಬಗ್ಗೆ (1/3)  $V_{CC}$  ,  $V_{CB}$  (ಅಥವಾ  $V_{CE}$ ) ಬಗ್ಗೆ (1/3)  $V_{CC}$ , ಮತ್ತು  $I_{C}R_{C}$  ಬಗ್ಗೆ (1/3)  $V_{CC}$  ಒಂದು ವಿನ್ಯಾಸ.  $I_E$  ಅನ್ನು  $\beta$  ನಲ್ಲಿನ ವ್ಯತ್ಯಾಸಗಳಿಗೆ ಸಂವೇದನಾರಹಿತವಾಗಿ ಮಾಡಲಾಗುತ್ತದೆ ಮತ್ತು  $R_B$  ಸಣ್ಣವನ್ನು ಆಯ್ಕೆ ಮಾಡುವ ಮೂಲಕ ಅದನ್ನು ತೃಪ್ತಿಪಡಿಸಬಹುದು. ಪ್ರತಿಯಾಗಿ R1 ಮತ್ತು R2 ಗಾಗಿ ಕಡಿಮೆ ಮೌಲ್ಯಗಳನ್ನು ಬಳಸುವ ಮೂಲಕ ಇದನ್ನು ಸಾಧಿಸಲಾಗುತ್ತದೆ. R1 ಮತ್ತು R2 ಗೆ ಕಡಿಮೆ ಮೌಲ್ಯಗಳು , ಆದರೂ, ವಿದ್ಯುತ್ ಪೂರೈಕೆಯಿಂದ ಹೆಚ್ಚಿನ ಪ್ರಸ್ತುತ ಡೈ್ರನ್ ಅರ್ಥೈಸುತ್ತದೆ, ಮತ್ತು ಆಂಪ್ಲಿಫೈಯರ್ನ ಇನ್ಫುಟ್ ಪ್ರತಿರೋಧವನ್ನು ಕಡಿಮೆ ಮಾಡಲು ಕಾರಣವಾಗುತ್ತದೆ (ಇನ್ಸುಟ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಬೇಸ್ಮೆ ಜೋಡಿಸಿದರೆ), ವಿನ್ಯಾಸದ ಈ ಭಾಗದಲ್ಲಿ ಒಳಗೊಂಡಿರುವ ಟ್ರೇಡ್-ಆಫ್ ಯಾವುದು. ನಾವು ಬೇಸ್ ಪೋಲ್ಬೇಜ್ ಅನ್ನು Vb ಯ ಮೌಲ್ಯದಿಂದ ಸ್ವತಂತ್ರವಾಗಿ ಮಾಡಲು ಬಯಸುತ್ತೇವೆ ಮತ್ತು ಪೋಲ್ಬೇಜ್ ವಿಭಜಕದಿಂದ ಮಾತ್ರ ನಿರ್ಧರಿಸುತ್ತುವೆ ಎಂದು ಗಮನಿಸಬೇಕು. ವಿಭಾಜಕದಲ್ಲಿನ ಪ್ರವಾಹವನ್ನು ಬೇಸ್ ಪ್ರವಾಹಕ್ಕಿಂತ ಹೆಚ್ಚು ದೊಡ್ಡದಾಗಿ ಮಾಡಿದರೆ ಇದು ಸ್ಪಪ್ಟವಾಗಿ ತೃಪ್ತಿಪಡುತ್ತದೆ. ಸಾಮಾನ್ಯವಾಗಿ ಒಬ್ಬರು R1 ಮತ್ತು R2 ಅಂತಹವುಗಳನ್ನು ಆಯ್ಕೆ ಮಾಡುತ್ತಾರೆ, ಅವುಗಳ ಪ್ರವಾಹವು  $I_E$  ನಿಂದ  $0.1I_E$  ರ ವ್ಯಾಪ್ತಿಯಲ್ಲಿರುತ್ತದೆ.

ಮೇಲಿನ ಫಿಗರ್ನ ಪಕ್ಷಪಾತದ ವ್ಯವಸ್ಥೆ ಡಿಸಿ ಹೊರಸೂಸುವ (ಮತ್ತು ಆದ್ದರಿಂದ ಸಂಗ್ರಾಹಕ) ಪ್ರವಾಹವನ್ನು ಸ್ಥಿರಗೊಳಿಸುವ ಕಾರ್ಯವಿಧಾನದ ಬಗ್ಗೆ ಹೆಚ್ಚಿನ ಒಳನೋಟವನ್ನು  $R_E$  ಒದಗಿಸಿದ ಪ್ರತಿಕ್ರಿಯೆ ಕ್ರಿಯೆಯನ್ನು ಪರಿಗಣಿಸುವ ಮೂಲಕ ಪಡೆಯಲಾಗುತ್ತದೆ. ಕೆಲವು ಕಾರಣಕ್ಕಾಗಿ ಹೊರಸೂಸುವ ಪ್ರವಾಹವು ಹೆಚ್ಚಾಗುತ್ತದೆ ಎಂದು ಪರಿಗಣಿಸಿ.  $R_E$  ಯಾದಂ್ಯತ ವೋಲ್ಟೇಜ್ ಡ್ರಾಪ್, ಮತ್ತು ಆದ್ದರಿಂದ ವಿಇ ಅನುಗುಣವಾದ ಹೆಚ್ಚಾಗುತ್ತದೆ. ಈಗ, ಬೇಸ್ ವೋಲ್ಟ್ ವಯಸ್ಸು ಪ್ರಾಥಮಿಕವಾಗಿ ವೋಲ್ಟೇಜ್ ವಿಭಾಜಕ R1 R2 ನಿರ್ಧರಿಸಲಾಗುತ್ತದೆ ವೇಳೆ, ಇದು  $R_B$  ಸಣ್ಣ ವೇಳೆ, ಇದು ಸ್ಥಿರವಾಗಿರುತ್ತದೆ, ಮತ್ತು ವಿಇ ಹೆಚ್ಚಳ ಅನುಗುಣವಾದ ಇಳಿಕೆಗೆ ಕಾರಣವಾಗುತ್ತದೆ ವಿಬಿಇ. ಇದು ಪ್ರತಿಯಾಗಿ ಸಂಗ್ರಾಹಕ (ಮತ್ತು ಹೊರಸೂಸುವ) ಪ್ರವಾಹವನ್ನು ಕಡಿಮೆ ಮಾಡುತ್ತದೆ, ಮೂಲತಃ ಊಹಿಸಿದ ಇದಕ್ಕೆ ವಿರುದ್ಧವಾದ ಬದಲಾವಣೆ. ಹೀಗಾಗಿ,  $R_E$  ಪಕ್ಷಪಾತ ಪ್ರವಾಹವನ್ನು ಸ್ಥಿರಗೊಳಿಸುವ ನಕಾರಾತ್ಮಕ ಪ್ರತಿಕ್ರಿಯೆ ಕ್ರಿಯೆಯನ್ನು ಒದಗಿಸುತ್ತದೆ.

पुरवठा व्होल्टेज व्हीसीसीच्या दिलेल्या मूल्यासाठी, आम्ही व्हीबीबीसाठी जितके जास्त मूल्य वापरतो, तितके कमी आरसी आणि कलेक्टर-बेस जंक्शन (व्हीसीबी) वर व्होल्टेजचे प्रमाण असेल. दुसरीकडे, आम्ही उच्च व्होल्टेज लाभ आणि मोठ्या सिग्नल स्विंग (ट्रान्सफॉर्मर कापून करण्यापूर्वी) प्राप्त करण्यासाठी आर. सी. ओलांडून व्होल्टेज मोठ्या प्रमाणात पाहिजे. आम्ही देखील एक मोठा सिग्नल स्विंग (ट्रान्सफॉर्मर संपृक्तता आधी) प्रदान करण्यासाठी VCB (किंवा VCE) मोठ्या इच्छित. अंगठ्याचा नियम म्हणून, VBB साठी एक डिझाइन (1/3) VCC बद्दल, VCB (किंवा VCE) बद्दल (1/3) VCC बद्दल, आणि ICRC बद्दल (1/3) VCC. आयई बी मधील विविधतांबद्दल असंवेदनशील केले जाते आणि आरबी लहान निवडून समाधानी होऊ शकते. यामधून R1 आणि R2 साठी कमी मूल्ये वापरून साध्य आहे. R1 आणि R2 साठी कमी मूल्ये , मात्र, वीज पुरवठा पासून उच्च चालू नाले याचा अर्थ असा होईल, आणि परिणामी वर्धकाचे इनपुट प्रतिकार कमी होईल (इनपुट सिग्नल बेसला जोडल्यास), जे डिझाइनच्या या भागामध्ये गुंतलेले ट्रेड-ऑफ आहे. हे लक्षात घेतले पाहिजे की आपल्याला बेस व्होल्टेज बीच्या मूल्यापासून स्वतंत्र बनवायचे आहे आणि व्होल्टेज डिव्हायडरद्वारे पूर्णपणे निर्धारित केले आहे. हे स्पष्टपणे विभाजीत मध्ये चालू बेस चालू पेक्षा खूप मोठे केले तर समाधानी होईल. साधारणपणे एक निवडतो R1 आणि R2 जसे की त्यांचे वर्तमान आयई ते 0.11ह च्या श्रेणीत आहे.

ज्या यंत्रणेद्वारे वरील आकृतीची पक्षपाती व्यवस्था डीसी उत्सर्जक (आणि म्हणूनच कलेक्टर) वर्तमान स्थिर करते त्याबाबतची अधिक माहिती आरई द्वारे प्रदान केलेल्या अभिप्राय कृतीचा विचार करून प्राप्त केली जाते. काही कारणास्तव emitter वर्तमान वाढते विचार करा. आरई ओलांडून व्होल्टेज ड्रॉप, आणि म्हणून VE संबंधित वाढ होईल. आता, बेस व्होल्ट वय प्रामुख्याने व्होल्टेज विभाजक R1 R2, जे आरबी लहान असेल तर केस आहे, तो सतत राहील, आणि VE मध्ये वाढ VBE मध्ये संबंधित कमी होईल. यामधून जिल्हाधिकारी (आणि emitter) वर्तमान कमी, मूळ गृहीत धरले की उलट बदल. त्यामुळे, आरई एक नकारात्मक अभिप्राय क्रिया प्रदान जे पूर्वग्रह वर्तमान स्थिर करते.

Example: To design the bias network for the amplifier in the below figure to establish a current  $I_E=1$  mA using a power supply  $V_{CC}=+12$  V. The transistor is specified to have a nominal  $\beta$  value of 100.

Solution: We shall follow the rule of thumb mentioned above and allocate one-third of the supply voltage to the voltage drop across R2 and another one-third to the voltage drop across Rc, leaving one-third for possible signal swing at the collector. Thus,

$$V_B = +4 \text{ V}$$

$$V_E = 4 - V_{BE} \simeq 3.3 \text{ V}$$

$$R_E = \frac{V_E}{I_E} = \frac{3.3}{1} = 3.3 \text{ k}\Omega$$

And R<sub>E</sub> is determined from

We select a voltage divider current of  $0.1I_E = 0.1 \text{ x } 1 = 0.1 \text{mA}$ . Neglecting the base current, we find

$$R_1 + R_2 = \frac{12}{0.1} = 120 \text{ k}\Omega$$

and

$$\frac{R_2}{R_1 + R_2} V_{CC} = 4 \text{ V}$$

Thus  $R_2 = 40 \text{ k}\Omega$  and  $R_1 = 80 \text{ k}\Omega$ .

Finding the value for I<sub>E</sub>

$$I_E = \frac{4 - 0.7}{3.3 + 0.027} = 0.99 \approx 1 \text{ mA}$$

And

$$R_C = \frac{12 - V_C}{I_C}$$

Substituting  $I_C = 0.99 \times 1 = 0.99 \text{mA}$ ,

$$R_C = \frac{12 - 8}{1} = 4 \,\mathrm{k}\Omega$$

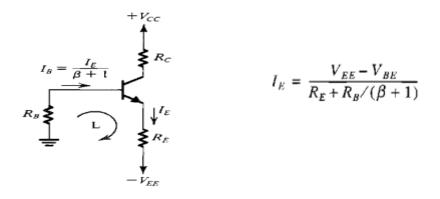

Note: If two power supplies are used for classical bias arrangement, then

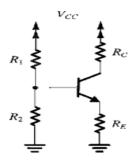

# 1.13 Biasing Using collector to base feedback bias:

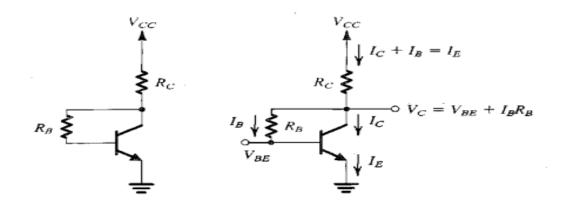

Figure below shows a simple but effective alternative biasing arrangement suitable for common-emitter amplifiers. The circuit employs a resistor R<sub>B</sub> connected between the collector and the base. Resistor R<sub>B</sub> provides negative feedback, which helps to stabilize the bias point of the BJT.

ಕೆಳಗಿನ ಚಿತ್ರವು ಸಾಮಾನ್ಯ-ಎಮಿಟರ್ ಆಂಪ್ಲಿಫೈಯರ್ಗಳಿಗೆ ಸೂಕ್ತವಾದ ಸರಳವಾದ ಆದರೆ ಪರಿಣಾಮಕಾರಿ ಪರ್ಯಾಯ ಪಕ್ಷಪಾತ ವ್ಯವಸ್ಥೆಯನ್ನು ತೋರಿಸುತ್ತದೆ. ಸರ್ಕ್ಯೂಟ್ ಸಂಗ್ರಾಹಕ ಮತ್ತು ಬೇಸ್ ನಡುವೆ ಸಂಪರ್ಕ ಒಂದು ನಿರೋಧಕ ಆರ್ಬಿ ನಿರೋಜಿಸುತ್ತದೆ. ಪ್ರತಿರೋಧಕ ಆರ್ಬಿ ನಕಾರಾತ್ಮಕ ಪ್ರತಿಕ್ರಿಯೆಯನ್ನು ಒದಗಿಸುತ್ತದೆ, ಇದು ಬಿಜೆಟಿಯ ಪಕ್ಷಪಾತ ಬಿಂದುವನ್ನು ಸ್ಥಿರಗೊಳಿಸಲು ಸಹಾಯ ಮಾಡುತ್ತದೆ.

खालील आकृती सामान्य-एमिटर वर्धकांसाठी योग्य एक साधी परंतु प्रभावी पर्यायी पक्षपाती व्यवस्था दर्शविते. सर्किट कलेक्टर आणि बेस दरम्यान कनेक्ट एक प्रतिरोधक आरबी रोजगार. रेसिस्टर आरबी नकारात्मक अभिप्राय प्रदान करते, जे बीजेटीच्या पक्षपाती बिंदूला स्थिर करण्यास मदत करते.

The circuit employs a resistor  $R_B$  connected between the collector and the base. Resistor  $R_B$  provides negative feedback, which helps to stabilize the bias point of the BJT.

Analysis: From fig(b) shows

$$\begin{split} V_{CC} &= I_E R_C + I_B R_B + V_{BE} \\ &= I_E R_C + \frac{I_E}{\beta + 1} R_B + V_{BE} \end{split}$$

Thus, the emitter current I<sub>E</sub> is

$$I_E = \frac{V_{CC} - V_{BE}}{R_C + R_B/(\beta + 1)}$$

given by

It follows that to obtain a value of  $I_E$  that is insensitive to variation of  $\beta$ , we select  $R_B / (\beta + 1)$  <<  $R_C$ . Note, however, that the value of  $R_B$  determines the allowable signal swing at the collector since

$$V_{CB} = I_B R_B = I_E \frac{R_B}{\beta + 1}$$

#### 1.2 SMALL SIGNAL OPERATIONS AND MODELS:

**Contents:** Collector current and Transconductance, Base current and input resistance, emitter current and input resistance, voltage gain, separating the signal and DC quantities, the hybrid  $\pi$  model and T model.

Having learned the basis for the operation of the BJT as an amplifier, we now take a closer look at the small-signal operation of the transistor. Toward that end, consider once more the conceptual amplifier circuit shown in Fig. 1(a). Here the base–emitter junction is forward biased by a dc voltage VBE (battery). The reverse bias of the collector–base junction is established by connecting the collector to another power supply of voltage VCC through a resistor RC. The input signal to be amplified is represented by the voltage source vbe that is superimposed on VBE. We consider first the dc bias conditions by setting the signal vbe to zero. The circuit reduces to that in Fig. 1(b), and we can write the following relationships for the dc currrents and voltages:

ಆಂಪ್ಲಿಫ್ ಯರ್ ಆಗಿ ಬಿಜೆಟಿಯ ಕಾರ್ಯಾಚರಣೆಯ ಆಧಾರವನ್ನು ಕಲಿತುಕೊಂಡ ನಾವು ಈಗ ಟ್ರಾನ್ಸಿಸ್ಟರ್ನ ಸಣ್ಣ-ಸಂಕೇತ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಹತ್ತಿರದಿಂದ ನೋಡುತ್ತೇವೆ. ಆತುದಿಗೆ, ಚಿತ್ರ 1 (ಎ) ನಲ್ಲಿ ತೋರಿಸಿರುವ ಪರಿಕಲ್ಪನಾ ಆಂಪ್ಲಿಫ್ ಯರ್ ಸರ್ಕ್ಯೂಟ್ ಅನ್ನು ಮತ್ತೊಮ್ಮೆ ಪರಿಗಣಿಸಿ. ಇಲ್ಲಿ ಬೇಸ್-ಎಮಿಟರ್ ಜಂಕ್ಷನ್ ಒಂದು ಡಿಸಿ ವೋಲ್ಟ್ ಪಿಬಿಇ (ಬ್ಯಾಟರಿ) ನಿಂದ ಮುಂದಕ್ಕೆ ಪಕ್ಷಪಾತ ಹೊಂದಿದೆ. ಸಂಗ್ರಾಹಕ-ಬೇಸ್ ಜಂಕ್ಷನ್ನ ಹಿಮ್ಮುಖ ಪಕ್ಷಪಾತವು ಸಂಗ್ರಾಹಕವನ್ನು ವೋಲ್ಟ್ ಪಿಪಿಸಿಯ ಮತ್ತೊಂದು ವಿದ್ಯುತ್ ಪೂರೈಕೆಗೆ ನಿರೋಧಕ ಆರ್ಸಿ ಮೂಲಕ ಸಂಪರ್ಕಿಸುವ ಮೂಲಕ ಸ್ಥಾಪಿಸಲ್ಪಡುತ್ತದೆ. ವರ್ಧಿಸಬೇಕಾದ ಇನ್ಫುಟ್ ಸಿಗ್ನಲ್ ಅನ್ನು ವಿಬಿಇ ಮೇಲೆ ಸೂಪರ್ಇಂಪೋಸ್ ಮಾಡಲಾದ ವೋಲ್ಟ್ ಪ್ ಮೂಲ ವಿಬಿ ಪ್ರತಿನಿಧಿಸುತ್ತದೆ. ಸಿಗ್ನಲ್ ವಿಬೆ ಶೂನ್ಯಕ್ಕೆ ಹೊಂದಿಸುವ ಮೂಲಕ ನಾವು ಮೊದಲು ಡಿಸಿ ಪಕ್ಷಪಾತ ಪರಿಸ್ಥಿತಿಗಳನ್ನು ಪರಿಗಣಿಸುತ್ತೇವೆ. ಸರ್ಕ್ಯೂಟ್ ಚಿತ್ರ 1 (ಬಿ) ನಲ್ಲಿ ಅದನ್ನು ಕಡಿಮೆ ಮಾಡುತ್ತದೆ, ಮತ್ತು ಡಿಸಿ ಕರೆಂಟ್ಗಳು ಮತ್ತು ವೋಲ್ಟ್ ಜ್ಗಳಿಗಾಗಿ ನಾವು ಕೆಳಗಿನ ಸಂಬಂಧಗಳನ್ನು ಬರೆಯಬಹುದು:

बीजेटीच्या ऑपरेशनचा आधार ॲम्प्लीफायर म्हणून जाणून घेतल्यानंतर, आम्ही आता ट्रान्झिस्टरच्या लहान-सिग्नल ऑपरेशनवर बारकाईने लक्ष देतो. त्या शेवटी, फिग 1 (एक) मध्ये दर्शविले वैचारिक वर्धक सिकेट पुन्हा एकदा विचार करा. येथे बेस-एमिटर जंक्शन पुढे डीसी व्होल्टेज VBE (बार्टरी) द्वारे पक्षपाती आहे. जिल्हाधिकारी-बेस जंक्शन उलट पूर्वग्रह एक प्रतिरोधक आरसी माध्यमातून व्होल्टेज VCC दसर्या

वीज पुरवठा जिल्हाधिकारी कनेक्ट करून स्थापना केली आहे. विस्तीर्ण करण्यासाठी इनपुट सिग्नल VBE वर superimposed आहे की व्होल्टेज स्रोत vbe द्वारे दर्शविले जाते. आपण सिग्नल vbe शून्य सेट करून प्रथम डीसी पूर्वग्रह अटी विचार. सर्किट Fig. 1 (ब) मध्ये त्या कमी होते, आणि आम्ही डीसी currents आणि व्होल्टेज खालील संबंध लिहू शकता:

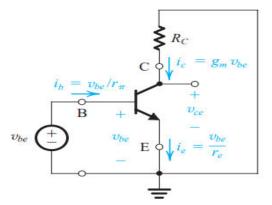

Fig 1(a) Conceptual circuit to illustrate the operation of the transistor as an amplifier. (b) The circuit of (a) with the signal source vbe eliminated for dc (bias) analysis.

$$I_B = I_C / \beta$$

$$V_{CE} = V_{CC} - I_C R_C$$

# 1.21 The Collector current and Transconductance:

If a signal vbe is applied as shown in Fig. 1(a), the total instantaneous base-emitter voltage vBE becomes

$$v_{BE} = V_{BE} + v_{be}$$

Correspondingly, the collector current becomes

$$i_C = I_S e^{v_{BE}/V_T} = I_S e^{(V_{BE} + v_{be})/V_T}$$

=  $I_S e^{V_{BE}/V_T} e^{v_{be}/V_T}$

$$i_C = I_C e^{v_{be}/V_T}$$

Now, if vbe << VT, we may approximate the above equation as,

$$i_C \simeq I_C \left( 1 + \frac{v_{be}}{V_T} \right)$$

Here we have expanded the exponential in  $i_C$  equation in a series and retained only the first two terms. This approximation, which is valid only for  $v_{be}$  less than approximately 10 mV, is referred to as the small-signal approximation. Under this approximation, the total collector current is given by the above equation and rewritten as

$$i_C = I_C + \frac{I_C}{V_T} v_{be}$$

Thus the collector current is composed of the dc bias value IC and a signal component ic

$$i_c = \frac{I_C}{V_T} v_{be}$$

This equation relates the signal current in the collector to the corresponding base–emitter signal voltage. It can be rewritten as

$i_c = g_m v_{be}$  where gm is called the transconductance,

$$g_m = \frac{I_C}{V_T}$$

We observe that the transconductance of the BJT is directly proportional to the collector bias current IC. Thus to obtain a constant predictable value for gm, we need a constant predictable IC. Finally, we note that BJTs have relatively high transconductance.

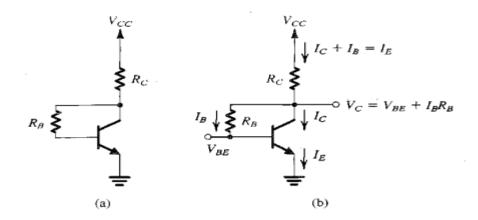

A graphical interpretation for gm is given in Fig.1( c ), where it is shown that gm is equal to the slope of the  $i_C$  – $v_{BE}$  characteristic curve at  $i_C$  =  $I_C$  (i.e., at the bias point Q). Thus,

$$g_m = \frac{\partial i_C}{\partial v_{BE}}\Big|_{i_C = I_C}$$

**Fig: 1(c):** Linear operation of the transistor under the small-signal condition: A small signal  $v_{be}$  with a triangular waveform is superimposed on the dc voltage  $V_{BE}$ . It gives rise to a collector signal current ic, also of triangular waveform, superimposed on the dc current  $I_C$ . Here,  $i_C = g_m v_{be}$ , where gm is the slope of the  $i_C - v_{BE}$  curve at the bias point Q.

The small-signal approximation implies keeping the signal amplitude sufficiently small that operation is restricted to an almost-linear segment of the iC–vBE exponential curve. Increasing the signal amplitude will result in the collector current having components nonlinearly related to vbe.

The analysis above suggests that for small signals ( $v_{be} \ll V_T$ ), the transistor behaves as a voltage-controlled current source. The input port of this controlled source is between base and emitter, and the output port is between collector and emitter. The transconductance of the controlled source is gm, and the output resistance is infinite. The latter ideal property is a result of our first-order model of transistor operation in which the collector voltage has no effect on the collector current in the active mode.

ಸಣ್ಣ-ಸಂಕೇತದ ಅಂದಾಜಿನ ಪ್ರಕಾರ, ಕಾರ್ಯಾಚರಣೆಯು ಐಸಿ-ವಿಬಿಇ ಫಾತಾಂಕ ವಕ್ರರೇಖೆಯ ಬಹುತೇಕ-ರೇಖೀಯ ವಿಭಾಗಕ್ಕೆ ಸೀಮಿತವಾಗಿದೆ ಎಂದು ಸಿಗ್ನಲ್ ವ್ಯಾಪ್ತಿಯನ್ನು ಸಾಕಪ್ಟು ಚಿಕ್ಕದಾಗಿ ಇಟ್ಟುಕೊಳ್ಳುವುದನ್ನು ಸೂಚಿಸುತ್ತದೆ. ಸಿಗ್ನಲ್ ವೈಶಾಲ್ಯವನ್ನು ಹೆಚ್ಚಿಸುವುದರಿಂದ ಸಂಗ್ರಾಹಕ ಪ್ರವಾಹವು ರೇಖಾತ್ಮಕವಲ್ಲದ ವಿಬೆಗೆ ಸಂಬಂಧಿಸಿದ ಘಟಕಗಳನ್ನು ಹೊಂದಿರುತ್ತದೆ.

ಮೇಲಿನ ವಿಶೇ್ಸಪಣೆಯು ಸಣ್ಣ ಸಂಕೇತಗಳಿಗೆ (ವಿಬಿ << ವಿಟಿ) ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಪೋಲ್ಟೇಜ್-ನಿಯಂತ್ರಿತ ಪ್ರಸ್ತುತ ಮೂಲವಾಗಿ ವರ್ತಿಸುತ್ತದೆ ಎಂದು ಸೂಚಿಸುತ್ತದೆ. ಈ ನಿಯಂತ್ರಿತ ಮೂಲದ ಇನ್ಫುಟ್ ಪೋರ್ಟ್ ಬೇಸ್ ಮತ್ತು ಎಮಿಟರ್ ನಡುವೆ ಇರುತ್ತದೆ, ಮತ್ತು ಔಟ್ಫುಟ್ ಪೋರ್ಟ್ ಸಂಗ್ರಾಹಕ ಮತ್ತು ಎಮಿಟರ್ ನಡುವೆ ಇರುತ್ತದೆ. ನಿಯಂತ್ರಿತ ಮೂಲದ ಟ್ರಾನಂ್ಸ್ಕಡಕ್ಷನ್ ಗ್ರಾಂ, ಮತ್ತು ಔಟ್ಫುಟ್ ಪ್ರತಿರೋಧ ಅನಂತ ಆಗಿದೆ. ನಂತರದ ಆದರ್ಶ ಆಸ್ತಿ ನಮ್ಮ ಮೊದಲ ಕ್ರಮಾಂಕದ ಮಾದರಿ ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಕಾರ್ಯಾಚರಣೆಯ ಪರಿಣಾಮವಾಗಿ ಇದರಲ್ಲಿ ಸಂಗ್ರಾಹಕ ಪೋಲ್ಟೇಜ್ ಸಕ್ರಿಯ ಮೋಡ್ನಲ್ಲಿ ಸಂಗ್ರಾಹಕ ಪ್ರವಾಹದ ಮೇಲೆ ಯಾವುದೇ ಪರಿಣಾಮ ಹೊಂದಿದೆ.

लहान-सिग्नल अंदाजे सिग्नल मोठेपणा पुरेसे लहान ठेवणे याचा अर्थ असा की ऑपरेशन IC-vBE घातांक वक्र एक जवळजवळ-रैखिक खंड मर्यादित आहे. संकेत मोठेपणा वाढत जिल्हाधिकारी चालू घटक nonlinearly vbe संबंधित असेल परिणाम होईल.

वरील विश्लेषण लहान सिग्नल (vbe << VT) साठी, ट्रान्झिस्टर एक व्होल्टेज नियंत्रित चालू स्रोत म्हणून वागतात असे सूचित करते की. या नियंत्रित स्रोताचे इनपुट पोर्ट बेस आणि एमिटर दरम्यान आहे, आणि आउटपुट पोर्ट कलेक्टर आणि एमिटर दरम्यान आहे. नियंत्रित स्रोताचे संक्रमण ग्रष्ट आहे, आणि आउटपुट प्रतिकार अनंत आहे. नंतरचे आदर्श गुणधर्म ट्रान्झिस्टर ऑपरेशन आमच्या पहिल्या ऑर्डर मॉडेल परिणाम आहे ज्यात कलेक्टर व्होल्टेज सक्रिय मोडमध्ये कलेक्टर वर्तमान वर परिणाम नाही.

# 1.22 The Base current and the input resistance at the Base:

To determine the resistance seen by v<sub>be</sub>, we first evaluate the total base current i<sub>B</sub>

$$i_B = \frac{i_C}{\beta} = \frac{I_C}{\beta} + \frac{1}{\beta} \frac{I_C}{V_T} v_{be}$$

**Thus**

$$i_B = I_B + i_b$$

where I<sub>B</sub> is equal to and the signal component i<sub>b</sub> is given by

$$i_b = \frac{1}{\beta} \frac{I_C}{V_T} v_{be}$$

Substituting for by g<sub>m</sub> gives

$$i_b = \frac{g_m}{\beta} v_{be}$$

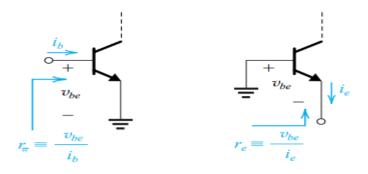

The small-signal input resistance between base and emitter, looking into the base, is denoted by  $r_{\pi}$  and is defined as

$$r_\pi \equiv \frac{v_{be}}{i_b}$$

Substituting for ib

$$r_{\pi} = \frac{\beta}{g_m}$$

Thus  $r_{\pi}$  is directly dependent on  $\beta$  and is inversely proportional to the bias current  $I_C$ . Substi $\gamma$  tuting for  $g_m$  and replacing  $I_C$  / $\beta$  by  $I_B$  gives an alternative expression for  $r_{\pi}$ ,

$$r_{\pi} = \frac{V_T}{I_B}$$

# 1.23 The Emitter Current and the input Resistance at the Emitter:

The total emitter current iE can be determined from

$$i_E = \frac{i_C}{\alpha} = \frac{I_C}{\alpha} + \frac{i_c}{\alpha}$$

Thus,

$$i_E = I_E + i_e$$

where  $I_E$  is equal to  $I_C/\alpha$  and the signal current  $i_e$  is given by

$$i_e = \frac{i_c}{\alpha} = \frac{I_C}{\alpha V_T} v_{be} = \frac{I_E}{V_T} v_{be}$$

If we denote the small-signal resistance between base and emitter looking into the emitter by  $r_{\text{e}}$ , it can be defined as

$$r_e \equiv \frac{v_{be}}{i_e}$$

we find that re, called the emitter resistance, is given by

$$r_e = \frac{V_T}{I_E}$$

Comparing with g<sub>m</sub> equation,

$$r_e = \frac{\alpha}{g_m} \simeq \frac{1}{g_m}$$

The relationship between  $r_{\pi}$  and  $r_{e}$

$$v_{be} = i_b r_\pi = i_e r_e$$

Thus,

$$r_{\pi} = (i_e/i_b)r_e$$

Which yeilds

$$r_{\pi} = (\beta + 1)r_e$$

Fig: 1(d): Illustrating the definition of  $r_{\pi}$  and  $r_{e}$

#### 1.24 Voltage Gain:

We have established above that the transistor senses the base–emitter signal  $v_{be}$  and causes a proportional current  $g_m$   $v_{be}$  to flow in the collector lead at a high (ideally infinite) impedance level. In this way the transistor is acting as a voltage-controlled current source. To obtain an output voltage signal, we may force this current to flow through a resistor, as is done in Fig. 1(a). Then the total collector voltage  $v_{CE}$  will be

ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಬೇಸ್-ಎಮಿಟರ್ ಸಿಗ್ನಲ್ ವ್ಯಾಬ್ ಅನ್ನು ಗ್ರಹಿಸುತ್ತದೆ ಮತ್ತು ಸಂಗ್ರಾಹಕ ಸೀಸದಲ್ಲಿ ಒಂದು ಅನುಪಾತದ ಪ್ರಸ್ತುತ ಗ್ರಾಂ ವ್ಯಾಬ್ ಅನ್ನು ಹೆಚ್ಚಿನ (ಆದರ್ಶವಾಗಿ ಅನಂತ) ಪ್ರತಿರೋಧ ಮಟ್ಟದಲ್ಲಿ ಹರಿಯುವಂತೆ ಮಾಡುತ್ತದೆ ಎಂದು ನಾವು ಮೇಲೆ ಸ್ಥಾಪಿಸಿದ್ದೇವೆ. ಈ ರೀತಿಯಲ್ಲಿ ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಪೋಲ್ಟೇಜ್ ನಿಯಂತ್ರಿತ ಪ್ರಸ್ತುತ ಮೂಲವಾಗಿ ಕಾರ್ಯನಿರ್ವಹಿಸುತ್ತಿದೆ. ಔಟ್ಫುಟ್ ಪೋಲ್ಟೇಜ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಪಡೆಯಲು, ನಾವು ಈ

ಪ್ರವಾಹವನ್ನು ರೆಸಿಸ್ಟರ್ ಮೂಲಕ ಹರಿಯುವಂತೆ ಒತ್ತಾಯಿಸಬಹುದು, ಚಿತ್ರ 1 (ಎ) ನಲ್ಲಿ ಮಾಡಿದಂತೆ. ನಂತರ ಒಟ್ಟು ಸಂಗ್ರಾಹಕ ಫೋಲ್ಮೇಜ್ ವಿಸಿಇ ಇರುತ್ತದೆ

आम्ही वर स्थापना केली आहे की ट्रान्झिस्टर बेस-एमिटर सिग्नल vbe इंद्रियगोचर आणि एक उच्च (आदर्श असीम) impedance पातळीवर जिल्हाधिकारी आघाडी मध्ये प्रवाह एक प्रमाणात चालू ग्र**ष्ट** vbe कारणीभूत. अशा प्रकारे ट्रान्झिस्टर एक व्होल्टेज नियंत्रित वर्तमान स्रोत म्हणून काम करत आहे. आऊटपुट व्होल्टेज सिग्नल प्राप्त करण्यासाठी, आम्ही या वर्तमानाला प्रतिरोधक माध्यमातून प्रवाह करण्यास भाग पाडू शकतो, जसे की अंजीर 1 (ए) मध्ये केले जाते. मग एकूण जिल्हाधिकारी व्होल्टेज vCE होईल

$$\begin{aligned} v_{CE} &= V_{CC} - i_C R_C \\ &= V_{CC} - (I_C + i_c) R_C \\ &= (V_{CC} - I_C R_C) - i_c R_C \\ &= V_{CE} - i_c R_C \end{aligned}$$

Here the quantity V<sub>CE</sub> is the dc bias voltage at the collector, and the signal voltage is given by

$$v_{ce} = -i_c R_C = -g_m v_{be} R_C$$

$$= (-g_m R_C) v_{be}$$

Thus the voltage gain of this amplifier Av is

$$A_v \equiv \frac{v_{ce}}{v_{he}} = -g_m R_C$$

Here again we note that because gm is directly proportional to the collector bias current, the gain will be as stable as the collector bias current is made. Substituting for gm enables us to express the gain in the form

$$A_v = -\frac{I_C R_C}{V_T}$$

#### 1.25 Seperating the signal and DC quantities:

The analysis above indicates that every current and voltage in the amplifier circuit of Fig.1(a) is composed of two components: a dc component and a signal component. For instance,  $v_{BE} = V_{BE} + v_{be}$ ,  $I_C = I_C + i_C$ , and so on. The dc components are determined from the dc circuit given in Fig. 1(b).

On the other hand, a representation of the signal operation of the BJT can be obtained by eliminating the dc sources, as shown below. Observe that since the voltage of an ideal dc supply does not change, the signal voltage across it will be zero. For this reason we have replaced  $V_{CC}$  and  $V_{BE}$  with short circuits. Had the circuit contained ideal dc current sources, these would have been replaced by open circuits.

ಮೇಲಿನ ವಿಶ್ಲೇಪಣೆಯು ಚಿತ್ರ 1 (ಎ) ಯ ಆಂಪ್ಲಿಫಯರ್ ಸರ್ಕ್ಯೂಟ್ನಲ್ಲಿನ ಪ್ರತಿಯೊಂದು ಪ್ರವಾಹ ಮತ್ತು ವೋಲ್ಟೇಜ್ ಎರಡು ಘಟಕಗಳಿಂದ ಕೂಡಿದೆ ಎಂದು ಸೂಚಿಸುತ್ತದೆ: ಡಿಸಿ ಘಟಕ ಮತ್ತು ಸಿಗ್ನಲ್ ಘಟಕ. ಉದಾಹರಣೆಗೆ, ವಿಬಿಇ ಮತ್ತು ವಿಬಿಇ + ವಿಬಿ, ಐಸಿ ಮತ್ತು ಐಸಿ + ಐಸಿ, ಮತ್ತು ಹಾಗೆ. dc ಘಟಕಗಳನ್ನು ಚಿತ್ರ 1 (ಬಿ) ನಲ್ಲಿ ನೀಡಿದ ಡಿಸಿ ಸರ್ಕ್ಯೂಟ್ನೆಂದ ನಿರ್ಧರಿಸಲಾಗುತ್ತದೆ.

ಮತ್ತೊಂದೆಡೆ, ಕೆಳಗೆ ತೋರಿಸಿರುವಂತೆ, ಡಿಸಿ ಮೂಲಗಳನ್ನು ತೆಗೆದುಹಾಕುವ ಮೂಲಕ ಬಿಜೆಟಿಯ ಸಿಗ್ನಲ್ ಕಾರ್ಯಾಚರಣೆಯ ಪ್ರಾತಿನಿಧ್ಯವನ್ನು ಪಡೆಯಬಹುದು. ಆದರ್ಶ ಡಿಸಿ ಪೂರೈಕೆಯ ವೋಲ್ಟೇಜ್ ಬದಲಾಗುವುದಿಲ್ಲವಾದ್ದರಿಂದ, ಅದರ ಉದ್ದಕ್ಕೂ ಸಿಗ್ನಲ್ ವೋಲ್ಟೇಜ್ ಶೂನ್ಯವಾಗಿರುತ್ತದೆ ಎಂದು ಗಮನಿಸಿ. ಈ ಕಾರಣಕ್ಕಾಗಿ ನಾವು ವಿಸಿಸಿ ಮತ್ತು ವಿಬಿಇ ಅನ್ನು ಶಾರ್ಟ್ ಸರ್ಕ್ಯೂಟ್ಗಳೊಂದಿಗೆ ಬದಲಾಯಿಸಿದ್ದೇವೆ. ಸರ್ಕ್ಯೂಟ್ ಆದರ್ಶ ಡಿಸಿ ಪ್ರಸ್ತುತ ಮೂಲಗಳನ್ನು ಹೊಂದಿದ್ದರೆ, ಇವುಗಳನ್ನು ತೆರೆದ ಸರ್ಕ್ಯೂಟ್ಗಳಿಂದ ಬದಲಾಯಿಸಲಾಗುತ್ತಿತ್ತು

वरील विश्लेषण Fig.1 (अ) च्या वर्धक सर्किट मध्ये प्रत्येक वर्तमान आणि व्होल्टेज दोन घटक बनलेले आहे असे सूचित करते की: एक डीसी घटक आणि एक सिग्नल घटक. उदाहरणार्थ, vBE = VBE + vbe, आयसी = आयसी + आयसी, आणि त्यामुळे वर. डीसी घटक फिग 1 (ब) मध्ये दिलेल्या डीसी सर्किट पासून निश्चित केले जातात.

दुसरीकडे, खाली दर्शविल्याप्रमाणे, डीसी स्रोत नष्ट करून भाजपच्या सिग्नल ऑपरेशनचे प्रतिनिधित्व मिळू शकते. एक आदर्श डीसी पुरवठ्याचा व्होल्टेज बदलत नाही म्हणून निरीक्षण करा, त्यावरील सिग्नल व्होल्टेज शून्य असेल. या कारणासाठी आम्ही VCC आणि VBE ची जागा शॉर्ट सर्किटने घेतली आहे. जर सर्किटमध्ये आदर्श डीसी वर्तमान स्रोत असते, तर हे खुल्या सर्किटद्वारे बदलले गेले असते.

Fig 1(e): The amplifier circuit of Fig. 1(a) with the dc sources ( $V_{BE}$  and  $V_{CC}$ ) eliminated (short-circuited). Thus, only the signal components are present. Note that this is a representation of the signal operation of the BJT and not an actual amplifier circuit.

Note, however, that the circuit of Fig. 1(e) is useful only in so far as it shows the various signal currents and voltages; it is not an actual amplifier circuit, since the dc bias circuit is not shown. Figure 6.39 also shows the expressions for the current increments ( $i_c$ ,  $i_b$ , and  $i_e$ ) obtained when a small signal  $v_{be}$  is applied. These relationships can be represented by a circuit. Such a circuit should have three terminals—C, B, and E—and should yield the same terminal currents indicated in Fig. 1(e). The resulting circuit is then equivalent to the transistor as far as small-signal operation is concerned, and thus it can be considered an equivalent small-signal circuit model.

ಆದಾಗ್ಯೂ, ಚಿತ್ರ 1 (ಇ) ಯ ಸರ್ಕ್ಯೂಟ್ ವಿವಿಧ ಸಿಗ್ನಲ್ ಪ್ರವಾಹಗಳು ಮತ್ತು ಪೋಲ್ಮೆಜ್ಗಳನ್ನು ತೋರಿಸುವವರೆಗೆ ಮಾತ್ರ ಉಪಯುಕ್ತವಾಗಿದೆ ಎಂಬುದನ್ನು ಗಮನಿಸಿ: ಇದು ನಿಜವಾದ ಆಂಪ್ಲಿಫಯರ್ ಸರ್ಕ್ಯೂಟ್ ಅಲ್ಲ, ಏಕೆಂದರೆ ಡಿಸಿ ಬಯಾಸ್ ಸರ್ಕ್ಯೂಟ್ ಅನ್ನು ತೋರಿಸಲಾಗಿಲ್ಲ. ಚಿತ್ರ 6.39 ಸಹ ಒಂದು ಸಣ್ಣ ಸಿಗ್ನಲ್ ವಿಬ್ ಅನ್ವಯಿಸಿದಾಗ ಪಡೆದ ಪ್ರಸ್ತುತ ವರ್ಧಕಗಳಿಗೆ (ic, ib, ಮತ್ತು ie) ಅಭಿವ್ಯಕ್ತಿಗಳು ತೋರಿಸುತ್ತದೆ. ಈ ಸಂಬಂಧಗಳನ್ನು ಸರ್ಕ್ಯೂಟ್ ಪ್ರತಿನಿಧಿಸಬಹುದು. ಅಂತಹ ಸರ್ಕ್ಯೂಟ್ ಮೂರು ಟರ್ಮಿನಲ್ಗಳನ್ನು ಹೊಂದಿರಬೇಕು - ಸಿ, ಬಿ, ಮತ್ತು ಇ - ಮತ್ತು ಚಿತ್ರ 1 (ಇ) ನಲ್ಲಿ ಸೂಚಿಸಲಾದ ಅದೇ ಟರ್ಮಿನಲ್ ಪ್ರವಾಹಗಳನ್ನು ನೀಡಬೇಕು. ಪರಿಣಾಮವಾಗಿ ಉಂಟಾಗುವ ಸರ್ಕ್ಯೂಟ್ ನಂತರ ಸಣ್ಣ-ಸಂಕೇತ ಕಾರ್ಯಾಚರಣೆಗೆ ಸಂಬಂಧಿಸಿದಂತೆ ಟ್ರಾನ್ಸಿಸ್ಟರ್ಗೆ ಸಮನಾಗಿರುತ್ತದೆ, ಮತ್ತು ಹೀಗಾಗಿ ಇದನ್ನು ಸಮಾನ ಸಣ್ಣ-ಸಂಕೇತ ಸರ್ಕ್ಯೂಟ್ ಮಾದರಿ ಎಂದು ಪರಿಗಣಿಸಬಹುದು.

तथापि, लक्षात घ्या की फिग. 1 (ई) चे सर्किट केवळ आतापर्यंत उपयुक्त आहे कारण ते विविध सिम्नल प्रवाह आणि व्होल्टेज दर्शविते; डीसी पूर्वग्रह सर्किट दर्शविले जात नाही म्हणून ते प्रत्यक्ष वर्धक सर्किट

नाही. आकृती 6.39 देखील एक लहान सिग्नल vbe लागू केले जाते तेव्हा प्राप्त वर्तमान वेतनवाढ (ic, ib, आणि म्हणजे) अभिव्यक्ती दाखवते. हे संबंध एक सर्किट द्वारे दर्शविले जाऊ शकते. अशा सर्किटमध्ये तीन टर्मिनल असावेत - सी, बी आणि ई - आणि फिग 1 (ई) मध्ये दर्शविलेले समान टर्मिनल प्रवाह उत्पन्न करावेत. परिणामी सर्किट नंतर लहान-सिग्नल ऑपरेशन पर्यंत ट्रान्झिस्टर समतुल्य आहे, आणि अशा प्रकारे तो एक समतुल्य लहान-सिग्नल सर्किट मॉडेल मानले जाऊ शकते.

# 1.26 The Hybrid – $\pi$ model:

An equivalent circuit model for the BJT is shown in Fig. 1(e). This model represents the BJT as a voltage-controlled current source and explicitly includes the input resistance looking into the base,  $r_{\pi}$ . The model obviously yields  $i_C = g_m \ v_{be}$  and Not so obvious, however, is the fact that the model also yields the correct expression for  $i_e$ . This can be shown as follows: At the emitter node we have

$$i_e = \frac{v_{be}}{r_{\pi}} + g_m v_{be} = \frac{v_{be}}{r_{\pi}} (1 + g_m r_{\pi})$$

$$= \frac{v_{be}}{r_{\pi}} (1 + \beta) = v_{be} / \left(\frac{r_{\pi}}{1 + \beta}\right)$$

$$= v_{be} / r_e$$

A slightly different equivalent-circuit model can be obtained by expressing the current of the controlled source  $(g_m \, v_{be})$  in terms of the base current  $i_b$  as follows:

$$g_{mv_{be}} = g_m(i_b r_\pi)$$

=  $(g_m r_\pi)i_b = \beta i_b$

This results in the alternative equivalent-circuit model shown in Fig.1(f). Here the transistor is represented as a current-controlled current source, with the control current being  $i_b$ .

Fig :Two slightly different versions of the hybrid- $\pi$  model for the small-signal operation of the BJT. The equivalent circuit in 1(e) represents the BJT as a voltage-controlled current source (transconductance amplifier), and that in 1(f) represents the BJT as a current-controlled current source (a current amplifier).

The two models of above figure are simplified versions of what is known as the hybrid- $\pi$  model. This is the most widely used model for the BJT. It is important to note that the small-signal equivalent circuits of fig 1(f) model the operation of the BJT at a given bias point. This should be obvious from the fact that the model parameters  $g_m$  and  $r_\pi$  depend on the value of the dc bias current  $I_C$ , as indicated in above figure. It is interesting and useful to note that the models of Fig. 1(e) and 1(f) are the small-signal versions of BJT.

ಮೇಲಿನ ಫಿಗರ್ನ ಎರಡು ಮಾದರಿಗಳು ಹೈಬ್ರಿಡ್-ಪಿ ಮಾದರಿ ಎಂದು ಕರೆಯಲ್ಪಡುವ ಸರಳೀಕೃತ ಆವೃತ್ತಿಗಳಾಗಿವೆ. ಇದು ಬಿಜೆಟಿಗೆ ಅತ್ಯಂತ ವ್ಯಾಪಕವಾಗಿ ಬಳಸಲಾಗುವ ಮಾದರಿಯಾಗಿದೆ. ಅಂಜೂರದ 1 (ಎಫ್) ಮಾದರಿಯ ಸಣ್ಣ-ಸಂಕೇತ ಸಮಾನ ಸರ್ಕ್ಯೂಟ್ಗಳು - ಒಂದು ನಿರ್ದಿಷ್ಟ ಪಕ್ಷಪಾತ ಬಿಂದುವಿನಲ್ಲಿ ಬಿಜೆಟಿಯ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಗಮನಿಸುವುದು ಮುಖ್ಯ. ಇದು ಮಾದರಿ ನಿಯತಾಂಕಗಳನ್ನು ಗ್ರಾಂ ಮತ್ತು rp ಮೇಲೆ ಚಿತ್ರದಲ್ಲಿ ಸೂಚಿಸಿರುವಂತೆ, dc ಪಕ್ಷಪಾತ ಪ್ರಸ್ತುತ IC ಮೌಲ್ಯವನ್ನು ಅವಲಂಬಿಸಿರುತ್ತದೆ ರಿಂದ ಸ್ಪಪ್ಟ ಇರಬೇಕು. ಚಿತ್ರ 1 (ಇ) ಮತ್ತು 1 (ಎಫ್) ನ ಮಾದರಿಗಳು ಬಿಜೆಟಿಯ ಸಣ್ಣ-ಸಂಕೇತ ಆವೃತ್ತಿಗಳಾಗಿವೆ ಎಂದು ಗಮನಿಸುವುದು ಆಸಕ್ತಿದಾಯಕ ಮತ್ತು ಉಪಯುಕ್ತವಾಗಿದೆ.

वरील आकृती दोन मॉडेल संकरीत-पी मॉडेल म्हणून ओळखले जाते काय सोपी आवृत्ती आहेत. भाजपसाठी हे सर्वात जास्त वापरले जाणारे मॉडेल आहे. हे लक्षात घेणे महत्वाचे आहे की अंजीर 1 (एफ) च्या लहान-सिग्नल समतुल्य सर्किट्स दिलेल्या पूर्वग्रह बिंदूवर BJT च्या ऑपरेशनचे मॉडेल करतात. हे मॉडेल मापदंड ग्रम आणि आरपी वरील आकृती मध्ये दर्शविल्याप्रमाणे डीसी पूर्वग्रह वर्तमान आयसी, मूल्य अवलंबून असते की पासून स्पष्ट पाहिजे. हे मनोरंजक आणि उपयुक्त आहे की फिग. 1 (ई) आणि 1 (एफ) च्या मॉडेल्स BJT च्या लहान-सिग्नल आवृत्ती आहेत.

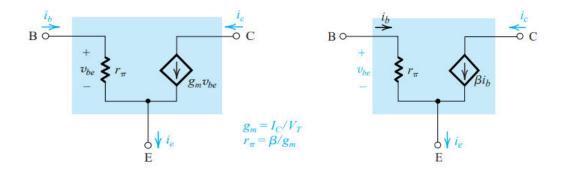

# **1.27 The T – Model:**

Although the hybrid- $\pi$  model can be used to carry out small-signal analysis of any transistor circuit, there are situations in which an alternative model, shown in Fig. 1(g), is much more

convenient. This model, called the T model, is shown in two versions below. The model of Fig. 1.g(a) represents the BJT as a voltage-controlled current source with the control voltage being vbe. Here, however, the resistance between base and emitter, looking into the emitter, is explicitly shown. From Fig. 1.g(a) we see clearly that the model yields the correct expressions for i<sub>C</sub> and i<sub>e</sub>. For i<sub>b</sub> we note that at the base node we have

ಹೈಬ್ರಿಡ್-ಪಿ ಮಾದರಿಯನ್ನು ಯಾವುದೇ ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಸರ್ಕ್ಯೂಟ್ನ ಸಣ್ಣ-ಸಂಕೇತ ವಿಶೇ್ಷಪಣೆಯನ್ನು ಕೈಗೊಳ್ಳಲು ಬಳಸಬಹುದಾದರೂ, ಚಿತ್ರಣದಲ್ಲಿ ತೋರಿಸಿರುವ ಪರ್ಯಾಯ ಮಾದರಿಯು ಸನ್ನಿವೇಶಗಳಿವೆ. 1 (ಜಿ), ಹೆಚ್ಚು ಅನುಕೂಲಕರ. ಟಿ ಮಾದರಿ ಎಂದು ಕರೆಯಲ್ಪಡುವ ಈ ಮಾದರಿಯನ್ನು ಕೆಳಗೆ ಎರಡು ಆವೃತ್ತಿಗಳಲ್ಲಿ ತೋರಿಸಲಾಗಿದೆ. ಚಿತ್ರ 1.g (ಎ) ಮಾದರಿಯು ಬಿಜೆಟಿಯನ್ನು ವೋಲ್ಟೇಜ್-ನಿಯಂತ್ರಿತ ಪ್ರವಾಹ ಮೂಲವಾಗಿ ಪ್ರತಿನಿಧಿಸುತ್ತದೆ. ಇಲ್ಲಿ, ಆದಾಗ್ಯೂ, ಬೇಸ್ ಮತ್ತು ಹೊರಸೂಸುವಿಕೆಯ ನಡುವಿನ ಪ್ರತಿರೋಧ, ಹೊರಸೂಸುವಿಕೆಯನ್ನು ನೋಡುವುದು, ಸ್ಪಪ್ಪವಾಗಿ ತೋರಿಸಲಾಗಿದೆ. ಫಿಗರ್ ನಿಂದ. 1.g(a) ಮಾದರಿ iC ಮತ್ತು ie ಗಾಗಿ ಸರಿಯಾದ ಅಭಿವ್ಯಕ್ತಿಗಳನ್ನು ನೀಡುತ್ತದೆ ಎಂದು ನಾವು ಸ್ಪಪ್ಪವಾಗಿ ನೋಡುತ್ತ್ವವೆ. ib ಗಾಗಿ ನಾವು ಹೊಂದಿರುವ ಬೇಸ್ ನೋಡ್ನಲ್ಲಿ ನಾವು ಗಮನಿಸುತ್ತ್ವವೆ

संकरीत-पी मॉडेल कोणत्याही ट्रान्झिस्टर सर्किट लहान-संकेत विश्लेषण अमलात आणणे वापरले जाऊ शकते तरी, अशा परिस्थितीत आहेत ज्यात एक पर्यायी मॉडेल, फिग मध्ये दर्शविले आहे. 1 (जी), जास्त सोयीस्कर आहे. हे मॉडेल, टी मॉडेल म्हणतात, खाली दोन आवृत्त्या मध्ये दर्शविले आहे. अंजीर मॉडेल. 1.g (एक) नियंत्रण व्होल्टेज vbe जात एक व्होल्टेज-नियंत्रित वर्तमान स्रोत म्हणून BJT प्रतिनिधित्व करते. तथापि, येथे, आधार आणि emitter दरम्यान प्रतिकार, emitter मध्ये पाहणे, स्पष्टपणे दर्शविले आहे. अंजीर पासून. 1.g (अ) आम्ही स्पष्टपणे पाहतो की मॉडेल आयसीसाठी योग्य अभिव्यक्ती उत्पन्न करते आणि म्हणजे. ib साठी आम्ही लक्षात ठेवा की बेस नोडमध्ये आपल्याकडे आहे

Figure 1(g): Two slightly different versions of what is known as the T model of the BJT. The circuit in 1(g)(a) is a voltage-controlled current source representation and that in 1(g)(b) is a current-controlled current source representation. These models explicitly show the emitter resistance re rather than the base resistance  $r\pi$  featured in the hybrid- $\pi$  model.

$$i_b = \frac{v_{be}}{r_e} - g_m v_{be} = \frac{v_{be}}{r_e} (1 - g_m r_e)$$

$$= \frac{v_{be}}{r_e} (1 - \alpha) = \frac{v_{be}}{r_e} \left( 1 - \frac{\beta}{\beta + 1} \right)$$

$$= \frac{v_{be}}{(\beta + 1)r_e} = \frac{v_{be}}{r_\pi}$$

If in the model of Fig. 1(g)(a) the current of the controlled source is expressed in terms of the emitter current as

$$g_m v_{be} = g_m (i_e r_e)$$

$$= (g_m r_e) i_e = \alpha i_e$$

we obtain the alternative T model shown in Fig. 1(g)(b). Here the BJT is represented as a current-controlled current source but with the control signal being  $i_e$ .

**MOSFETs**: Biasing in MOS amplifier circuits: Fixing VGS, Fixing VG, Drain to Gate feedback resistor. Small signal operation and modeling: The DC bias point, signal current in drain, voltage gain, small signal equivalent circuit models, transconductance, The T equivalent circuit model.

#### 1.3 Biasing in MOS Amplifier Circuits:

An essential step in the design of a MOSFET amplifier circuit is the establishment of an appropriate dc operating point for the transistor. This is the step known as biasing or bias design. An appropriate dc operating point or bias point is characterized by a stable and predictable dc drain current I<sub>D</sub> and by a dc drain-to-source voltage V<sub>DS</sub> that ensures operation in the saturation region for all expected input-signal levels.

ಎಂಒಎಸ್ಎಫ್ಇಟಿ ಆಂಪ್ಲಿಫಯರ್ ಸರ್ಕ್ಯೂಟ್ನ ವಿನ್ಯಾಸದಲ್ಲಿ ಒಂದು ಅತ್ಯಗತ್ಯ ಹಂತವೆಂದರೆ ಟ್ರಾನ್ಸಿಸ್ಟರ್ಗೆ ಸೂಕ್ತವಾದ ಡಿಸಿ ಆಪರೇಟಿಂಗ್ ಪಾಯಿಂಟ್ ಅನ್ನು ಸ್ಥಾಪಿಸುವುದು. ಇದು ಪಕ್ಷಪಾತ ಅಥವಾ ಪಕ್ಷಪಾತ ವಿನ್ಯಾಸ ಎಂದು ಕರೆಯಲ್ಪಡುವ

ಹಂತವಾಗಿದೆ. ಸೂಕ್ತ ಡಿಸಿ ಆಪರೇಟಿಂಗ್ ಪಾಯಿಂಟ್ ಅಥವಾ ಪಕ್ಷಪಾತ ಬಿಂದುವನ್ನು ಸ್ಥಿರ ಮತ್ತು ಊಹಿಸಬಹುದಾದ ಡಿಸಿ ಡೈ್ರನ್ ಕರೆಂಟ್ ಐಡಿ ಮತ್ತು ಡಿಸಿ ಡೈ್ರನ್-ಟು-ಸೋರ್ಸ್ ಪೋಲ್ಟೇಜ್ ವಿಡಿಎಸ್ನಿಂದ ನಿರೂಪಿಸಲಾಗಿದೆ, ಇದು ಎಲ್ಲಾ ನಿರೀಕ್ಷಿತ ಇನ್ಫುಟ್-ಸಿಗ್ನಲ್ ಮಟ್ಟಗಳಿಗೆ ಸ್ಯಾಚುರೇಶನ್ ಪ್ರದೇಶದಲ್ಲಿ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಖಾತ್ರಿಗೊಳಿಸುತ್ತದೆ.

एमओएसएफईटी वर्धक सर्किटच्या डिझाइनमध्ये एक आवश्यक पाऊल म्हणजे ट्रान्झिस्टरसाठी योग्य डीसी ऑपरेटिंग पॉईंटची स्थापना. हे पाऊल पक्षपाती किंवा पक्षपाती डिझाइन म्हणून ओळखले जाते. एक योग्य डीसी ऑपरेटिंग पॉईंट किंवा पूर्वग्रह बिंदू एक स्थिर आणि अंदाज डीसी ड्रेन करंट आयडी आणि डीसी ड्रेन-टू-सोर्स व्होल्टेज व्हीडीएस द्वारे दर्शविले जाते जे सर्व अपेक्षित इनपुट-सिग्नल स्तरांसाठी संपुक्तता प्रदेशात ऑपरेशन सुनिश्चित करते.

# 1.31 Biasing by Fixing $V_{GS}$ :

The most straightforward approach to biasing a MOSFET is to fix its gate-to-source voltage  $V_{GS}$  to the value required to provide the desired  $I_D$ . This voltage value can be derived from the power-supply voltage  $V_{DD}$  through the use of an appropriate voltage divider. Alternatively, it can be derived from another suitable reference voltage that might be available in the system. Independent of how the voltage VGS may be generated, this is not a good approach to biasing a MOSFET. To understand the reason for this statement, recall that  $v_{CD} = v_{CD} = v_$

एक MOSFET पक्षपाती सर्वात सरळ दृष्टिकोन इच्छित आयडी प्रदान करण्यासाठी आवश्यक मूल्य त्याच्या गेट-टू-स्रोत व्होल्टेज VGS निराकरण करण्यासाठी आहे. हे व्होल्टेज मूल्य योग्य व्होल्टेज विभाजक वापर माध्यमातून वीज पुरवठा व्होल्टेज VDD पासून प्राप्त केले जाऊ शकते. पर्यायाने, तो

प्रणाली मध्ये उपलब्ध असू शकते की दुसर्या योग्य संदर्भ व्होल्टेज पासून प्राप्त केले जाऊ शकते. व्होल्टेज व्हीजीएस कसे तयार केले जाऊ शकते यापासून स्वतंत्र, हे एक MOSFET पक्षपाती करण्याचा चांगला दृष्टिकोन नाही. या विधानाचे कारण समजून घेण्यासाठी, ते लक्षात ठेवा

$$I_D = \frac{1}{2} \mu_n C_{ox} \frac{W}{L} (V_{GS} - V_t)^2$$

and note that the values of the threshold voltage  $V_t$ , the oxide-capacitance  $C_{OX}$ , and (to a lesser extent) the transistor aspect ratio vary widely among devices of supposedly the same size and type. This is certainly the case for discrete devices, in which large spreads in the values of these parameters occur among devices of the same manufacturer's part number. The spread is also large in integrated circuits, especially among devices fabricated on different wafers and certainly between different batches of wafers. Furthermore, both Vt and  $\mu_n$  depend on temperature, with the result that if we fix the value of  $V_{GS}$ , the drain current  $I_D$  becomes very much temperature dependent.

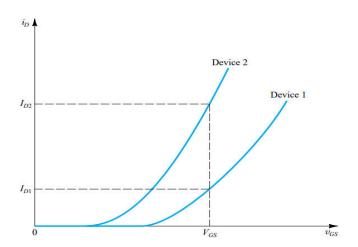

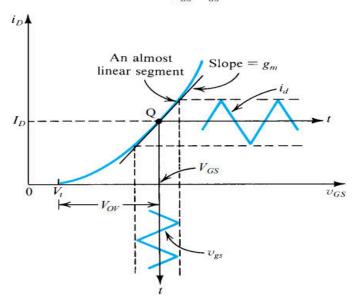

To emphasize the point that biasing by fixing  $V_{GS}$  is not a good technique, we show in Fig. 1(h) two  $i_{D}$ – $v_{GS}$  characteristic curves representing extreme values in a batch of MOSFETs of the same type. Observe that for the fixed value of  $V_{GS}$ , the resultant spread in the values of the drain current can be substantial.

**Fig:1(h):** The use of fixed bias (constant  $V_{GS}$ ) can result in a large variability in the value of  $I_D$ . Devices 1 and 2 represent extremes among units of the same type.

# 1.32 Biasing By fixing V<sub>G</sub> and connecting a Resistance in the source:

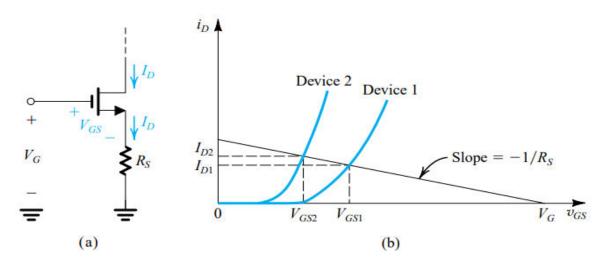

An excellent biasing technique for discrete MOSFET circuits consists of fixing the dc voltage at the gate,  $V_G$ , and connecting a resistance in the source lead, as shown in Fig. 1(i). For this circuit we can write

$$V_G = V_{GS} + R_S I_D$$

Now, if  $V_G$  is much greater than  $V_{GS}$ ,  $I_D$  will be mostly determined by the values of  $V_G$  and R=S. However, even if  $V_G$  is not much larger than  $V_{GS}$ , resistor  $R_S$  provides negative feedback, which acts to stabilize the value of the bias current  $I_D$ . To see how this comes about, consider what happens when  $I_D$  increases for whatever reason. Equation above indicates that since  $V_G$  is constant,  $V_{GS}$  will have to decrease. This in turn results in a decrease in  $I_D$ , a change that is

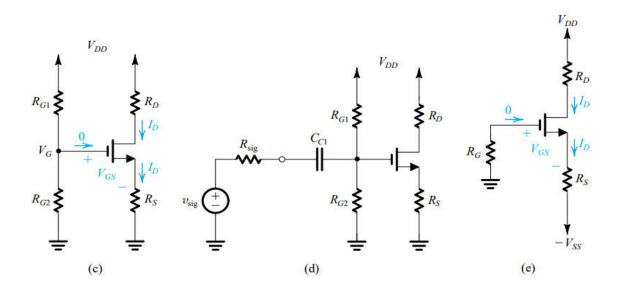

Fig 1(i):Biasing using a fixed voltage at the gate, VG, and a resistance in the source lead, RS: (a) basic arrangement; (b) reduced variability in ID; (c) practical implementation using a single supply; (d) coupling of a signal source to the gate using a capacitor CC1; (e) practical implementation using two supplies.

opposite to that initially assumed. Thus the action of RS works to keep ID as constant as possible. This negative feedback action of RS gives it the name degeneration resistance, a name that we will appreciate much better at a later point in this text.

Figure (b) provides a graphical illustration of the effectiveness of this biasing scheme. Here too we show the  $i_D$ – $v_{GS}$  characteristics for two devices that represent the extremes of a batch of MOSFETs. Superimposed on the device characteristics is a straight line that represents the constraint imposed by the bias circuit. The intersection of this straight line with the  $i_D$ – $v_{GS}$  characteristic curve provides the coordinates ( $I_D$  and  $V_{GS}$ ) of the bias point. Observe that compared to the case of fixed  $V_{GS}$ , here the variability obtained in  $I_D$  is much smaller. Also, note that the variability decreases as  $V_G$  and  $R_S$  are made larger (thus providing a bias line that is less steep).

Two possible practical discrete implementations of this bias scheme are shown in Fig. (c) and (e). The circuit in Fig. (c) utilizes one power-supply  $V_{DD}$  and derives  $V_G$  through a voltage divider ( $R_{G1}$ ,  $R_{G2}$ ). Since  $I_G = 0$ ,  $R_{G1}$  and  $R_{G2}$  can be selected to be very large (in the megohm range), allowing the MOSFET to present a large input resistance to a signal source that may be connected to the gate through a coupling capacitor, as shown in Fig.(d). Here capacitor  $C_{C1}$  blocks dc and thus allows us to couple the signal vsig to the amplifier input without disturbing the MOSFET dc bias point. The value of CC1 should be selected large enough to approximate a short circuit at all signal frequencies of interest. We shall study capacitively coupled MOSFET amplifiers, which are suitable only in discrete circuit design. Finally, note that in the circuit of Fig.(c), resistor  $R_D$  is selected to be as large as possible to obtain high gain but small enough to allow for the desired signal swing at the drain while keeping the MOSFET in saturation at all times.

When two power supplies are available, as is often the case, the somewhat simpler bias arrangement of Fig.(e) can be utilized. This circuit is an implementation of above equation, with  $V_G$  replaced by  $V_{SS}$ . Resistor  $R_G$  establishes a dc ground at the gate and presents a high input resistance to a signal source that may be connected to the gate through a coupling capacitor.

#### 1.33 Biasing Using Drain to Gate Feedback Resistor:

A simple and effective discrete-circuit biasing arrangement utilizing a feedback resistor connected between the drain and the gate is shown in Fig. 1(j). Here the large feedback

resistance  $R_G$  (usually in the megohm range) forces the dc voltage at the gate to be equal to that at the drain (because  $I_G = 0$ ). Thus we can write

$$V_{GS} = V_{DS} = V_{DD} - R_D I_D$$

which can be rewritten in the form

$$V_{DD} = V_{GS} + R_D I_D$$

If  $I_D$  for some reason changes, say increases, then above equation indicates that  $V_{GS}$  must decrease. The decrease in  $V_{GS}$  in turn causes a decrease in  $I_D$ , a change that is opposite in direction to the one originally assumed. Thus the negative feedback or degeneration provided by  $R_G$  works to keep the value of  $I_D$  as constant as possible. The circuit of Fig. 1(k) can be utilized as an amplifier by applying the input voltage signal to the gate via a coupling capacitor so as not to disturb the dc bias conditions already established. The amplified output signal at the drain can be coupled to another part of the circuit, again via a capacitor.

Fig:1(j): Biasing the MOSFET using a large drain-to-gate feedback resistance,  $R_{\rm G}$

**Small signal operation and modelling**: The DC bias point, signal current in drain, voltage gain, small signal equivalent circuit models, transconductance, The T equivalent circuit model.

# 1.4 Small Signal Operation and Models:

In our study of the operation of the MOSFET amplifier we learned that linear amplification can be obtained by biasing the MOSFET to operate in the saturation region and by keeping the input signal small. In this section, we explore the small-signal operation in some detail.

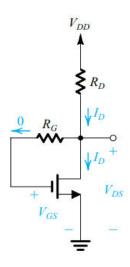

For this purpose we utilize the conceptual amplifier circuit shown in Fig.1(k). Here the MOS transistor is biased by applying a dc voltage  $V_{GS}$ , and the input signal to be amplified,  $v_{gs}$ , is superimposed on the dc bias voltage  $V_{GS}$ . The output voltage is taken at the drain.

ಮೋಸ್ಫೆಟ್ ಆಂಪ್ಲಿಫೈಯರ್ನ ಕಾರ್ಯಾಚರಣೆಯ ನಮ್ಮ ಅಧ್ಯಯನದಲ್ಲಿ ನಾವು ಸ್ಯಾಚುರೇಶನ್ ಪ್ರದೇಶದಲ್ಲಿ ಕಾರ್ಯನಿರ್ವಹಿಸಲು ಮೋಸ್ಫೆಟ್ ಅನ್ನು ಪಕ್ಷಪಾತ ಮಾಡುವ

ಮೂಲಕ ಮತ್ತು ಇನ್ಪುಟ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಚಿಕ್ಕದಾಗಿ ಇಟ್ಟುಕೊಳ್ಳುವ ಮೂಲಕ ರೇಖೀಯ ವರ್ಧನೆಯನ್ನು ಪಡೆಯಬಹುದು ಎಂದು ನಾವು ಕಲಿತಿದ್ದೇವೆ. ಈ ವಿಭಾಗದಲ್ಲಿ, ನಾವು ಕೆಲವು ವಿವರವಾಗಿ ಸಣ್ಣ-ಸಿಗ್ನಲ್ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಅನ್ನೇಷಿಸುತ್ತುವೆ.

ಈ ಉದ್ದೇಶಕ್ಕಾಗಿ ನಾವು ಪರಿಕಲ್ಪನೆಯ ಆಂಪ್ಲಿಫಯರ್ ಸರ್ಕ್ಯೂಟ್ ಅನ್ನು ಚಿತ್ರ 1 (ಕೆ) ನಲ್ಲಿ ತೋರಿಸಲಾಗಿದೆ ಬಳಸಿಕೊಳ್ಳುತ್ತುವೆ. ಇಲ್ಲಿ ಡಿಸಿ ವೋಲ್ಟೇಜ್ ವಿಜಿಎಸ್ ಅನ್ನು ಅನ್ವಯಿಸುವ ಮೂಲಕ ಎಂಒಎಸ್ ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಪಕ್ಷಪಾತಿಯಾಗಿದೆ, ಮತ್ತು ವರ್ಧಿಸಬೇಕಾದ ಇನ್ಪುಟ್ ಸಿಗ್ನಲ್, ವಿಜಿಎಸ್, ಡಿಸಿ ಪಕ್ಷಪಾತ ವೋಲ್ಟೇಜ್ ವಿಜಿಎಸ್ ಮೇಲೆ ಸೂಪರ್ಇಂಪೋಸ್ ಆಗಿದೆ. ಔಟ್ಫುಟ್ ವೋಲ್ಟೇಜ್ ಡೈನ್ ನಲ್ಲಿ ತೆಗೆದುಕೊಳ್ಳಲಾಗುತ್ತದೆ

एमओएसएफईटी वर्धकाच्या ऑपरेशनच्या आमच्या अभ्यासात आम्ही शिकलो की संपृक्तता क्षेत्रात कार्य करण्यासाठी एमओएसएफईटीला पक्षपाती करून आणि इनपुट सिग्नल लहान ठेवून रेषेचा विस्तार प्राप्त केला जाऊ शकतो. या विभागात, आम्ही काही तपशील मध्ये लहान-संकेत ऑपरेशन अन्वेषण.

या कारणासाठी आम्ही Fig.1 (के) मध्ये दर्शविले वैचारिक वर्धक सर्किट वापर. येथे एमओएस ट्रान्झिस्टर डीसी व्होल्टेज VGS लागू करून पक्षपाती आहे, आणि इनपुट सिग्नल प्रवर्धित करणे, vgs, डीसी पक्षपाती व्होल्टेज VGS वर superimposed आहे. आउटपुट व्होल्टेज नाले येथे घेतले जाते.

# 1.41 The DC Bias point:

The dc bias current ID can be found by setting the signal vgs to zero; thus,

$$I_D = \frac{1}{2} k_n (V_{GS} - V_t)^2 = \frac{1}{2} k_n V_{OV}^2$$

where we have neglected channel-length modulation (i.e., we have assumed  $\lambda=0$ ). Here  $V_{OV}=V_{GS}-V_t$  is the overdrive voltage at which the MOSFET is biased to operate. The dc voltage at the drain  $V_{DS}$  will be  $V_{DS}=V_{DD}-R_DI_D$ .

Fig 1(k): Conceptual circuit utilized to study the operation of the MOSFET as a small-signal amplifier.

To ensure saturation-region operation, we must have

$$V_{DS} > V_{OV}$$

Furthermore, since the total voltage at the drain will have a signal component superimposed on  $V_{DS}$ ,  $V_{DS}$  has to be sufficiently greater than  $(V_{OV})$  to allow for the required signal swing.

# 1.42 The signal current in the Drain terminal:

Next, consider the situation with the input signal vgs applied. The total instantaneous gate-to<sub>7</sub> source voltage will be

$$v_{GS} = V_{GS} + v_{gs}$$

resulting in a total instantaneous drain current i<sub>D</sub>,

$$\begin{split} i_D &= \frac{1}{2} k_n (V_{GS} + v_{gs} - V_t)^2 \\ &= \frac{1}{2} k_n (V_{GS} - V_t)^2 + k_n (V_{GS} - V_t) v_{gs} + \frac{1}{2} k_n v_{gs}^2 \end{split}$$

The first term on the above equation can be recognized as the dc bias current  $I_D$ . The second term represents a current component that is directly proportional to the input signal  $v_{gs}$ . The third term is a current component that is proportional to the square of the input signal. This last component is undesirable because it represents nonlinear distortion. To reduce the nonlinear distortion introduced by the MOSFET, the input signal should be kept small so that

$$\frac{1}{2}k_n v_{gs}^2 \ll k_n (V_{GS} - V_t) v_{gs}$$

Resulting in

$$v_{\sigma s} \ll 2(V_{GS} - V_t)$$

Or equivalently

$$v_{os} \ll 2V_{OV}$$

If this small-signal condition is satisfied, we may neglect the last term in Equation of  $i_D$  and express  $i_D$  as

$$i_D \simeq I_D + i_d$$

Where

$$i_d = k_n (V_{GS} - V_t) v_{gs}$$

Or in terms of overdrive voltage V<sub>OV</sub>

$$g_m = k_n V_{OV}$$

The parameter that relates  $i_d$  and  $v_{gs}$  is the MOSFET transconductance  $g_m$ ,

$$g_m \equiv \frac{i_d}{v_{gs}} = k_n (V_{GS} - V_t)$$

Or

$$g_m = k_n V_{OV}$$

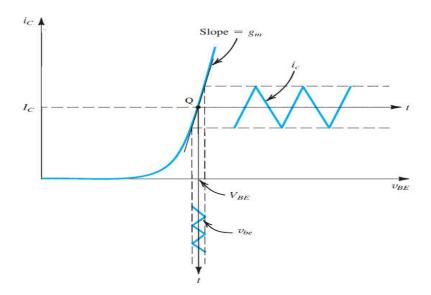

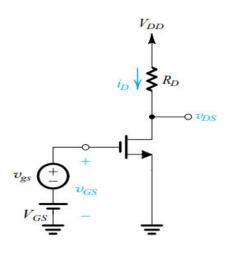

Figure below presents a graphical interpretation of the small-signal operation of the MOSFET amplifier. Note that  $g_m$  is equal to the slope of the  $i_D - v_{GS}$  characteristic at the bias point,

$$g_m \equiv \frac{\partial i_D}{\partial v_{GS}}\bigg|_{v_{GS} = V_{GS}}$$

Fig:1(1): Small-signal operation of the MOSFET amplifier.

# 1.43 The Voltage Gain:

we can express the total instantaneous drain voltage v<sub>DS</sub> as follows:

$$v_{DS} = V_{DD} - R_D i_D$$

Under the small-signal condition, we have

$$v_{DS} = V_{DD} - R_D(I_D + i_d)$$

Which can be rewritten as

$$v_{DS} = V_{DS} - R_D i_d$$

Thus the signal component of the drain voltage is

$$v_{ds} = -i_d R_D = -g_m v_{gs} R_D$$

Which indicates that the voltage gain is given by

$$A_v \equiv \frac{v_{ds}}{v_{gs}} = -g_m R_D$$

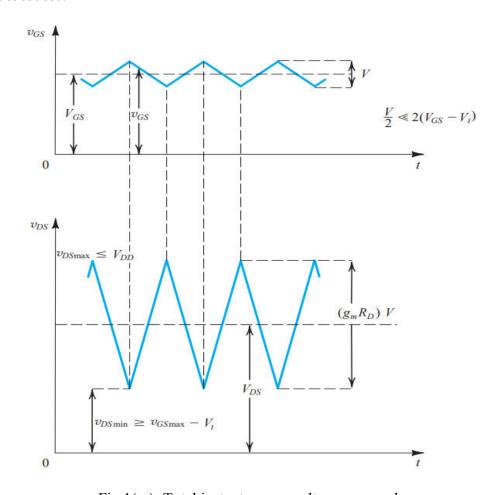

The minus sign in above equation indicates that the output signal  $v_{ds}$  is  $180^{\circ}$  out of phase with respect to the input signal  $v_{gs}$ . The input signal is assumed to have a triangular waveform with an amplitude much smaller than  $2(V_{GS}-V_t)$ , the small-signal condition ensure linear operation. For operation in the saturation region at all times, the minimum value of  $v_{DS}$  should not fall below the corresponding value of  $v_{GS}$  by more than  $V_t$ . Also, the maximum value of  $v_{DS}$  should be smaller than  $V_{DD}$ ; otherwise the FET will enter the cutoff region and the peaks of the output signal waveform will be clipped off.

ಮೇಲಿನ ಸಮೀಕರಣದಲ್ಲಿ ಮೈನಸ್ ಸೈನ್ ಇನ್ಫುಟ್ ಸಿಗ್ನಲ್ ವ್ಹ್ಸ್ ಸಂಬಂಧಿಸಿದಂತೆ ಔಟ್ಫುಟ್ ಸಿಗ್ನಲ್ 180deg ಔಟ್ ಹಂತದ ಎಂದು ಸೂಚಿಸುತ್ತದೆ. ಇನ್ಫುಟ್ ಸಿಗ್ನಲ್ ಅನ್ನು 2 (ವಿಜಿಎಸ್ - ವಿಟಿ ) ಗಿಂತ ಚಿಕ್ಕದಾದ ವೈಶಾಲ್ಯದೊಂದಿಗೆ ತ್ರಿಕೋನ ತರಂಗರೂಪವನ್ನು ಹೊಂದಿದೆ ಎಂದು ಊಹಿಸಲಾಗಿದೆ, ಸಣ್ಣ-ಸಿಗ್ನಲ್ ಪರತ್ತು ರೇಖೀಯ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಖಚಿತಪಡಿಸುತ್ತದೆ. ಎಲ್ಲಾ ಸಮಯದಲ್ಲೂ ಸ್ಯಾಚುರೇಶನ್ ಪ್ರದೇಶದಲ್ಲಿನ ಕಾರ್ಯಾಚರಣೆಗಾಗಿ, ವಿಡಿಎಸ್ನ ಕನಿಪ್ಪ ಮೌಲ್ಯವು ವಿಜಿಎಸ್ನ ಕೋರ್ ಸ್ಫಾಂಡಿಂಗ್ ಮೌಲ್ಯಕ್ಕಿಂತ ವಿಟಿಗಿಂತ ಹೆಚ್ಚು ಕೆಳಗೆ ಬೀಳಬಾರದು. ಅಲ್ಲದೆ, ವಿಡಿಎಸ್ನ ಗರಿಪ್ಮ ಮೌಲ್ಯವು ವಿಡಿಡಿಎಕ್ಸ್ಗಿಂತ ಚಿಕ್ಕದಾಗಿರಬೇಕು - ಇಲ್ಲದಿದ್ದರೆ ಎಫ್ಇಟಿ ಕಟ್ಆಫ್ ಪ್ರದೇಶವನ್ನು ಪ್ರವೇಶಿಸುತ್ತದೆ ಮತ್ತು ಔಟ್ಫುಟ್ ಸಿಗ್ನಲ್ ತರಂಗ ರೂಪದ ಶಿಖರಗಳನ್ನು ಕ್ಲಿಫ್ ಮಾಡಲಾಗುವುದು.

वरील समीकरण मध्ये वजा चिन्ह इनपुट सिग्नल vgs संदर्भात उत्पादन सिग्नल vds टप्प्यात बाहेर 180deg आहे असे सूचित करते की. इनपुट सिग्नल 2 (व्हीजीएस - व्हीटी) पेक्षा खूपच लहान आयामासह त्रिकोणी तरंग असल्याचे गृहित धरले जाते, लहान-सिग्नल स्थिती रेषेचा ऑपरेशन सुनिश्चित करते. प्रत्येक वेळी संपृक्तता प्रदेशात ऑपरेशनसाठी, व्हीडीएसचे किमान मूल्य व्हीजीएसच्या कोरे स्पोंडिंग मूल्यापेक्षा अधिक व्हीटीने खाली येऊ नये. तसेच, व्हीडीएसचे जास्तीत जास्त मूल्य व्हीडीडीपेक्षा लहान असावे; अन्यथा एफईटी कटऑफ प्रदेशात प्रवेश करेल आणि आउटपुट सिग्नल लहर फॉर्मची शिखरे कापली जातील.

# Seperating DC Analysis and Signal Analysis:

From the preceding analysis, we see that under the small-signal approximation, signal quantities are superimposed on dc quantities. For instance, the total drain current  $i_D$  equals the dc current  $I_D$  plus the signal current  $i_d$ , the total drain voltage  $v_{DS} = V_{DS} + v_{ds}$ , and so on. It follows that the analysis and design can be greatly simplified by separating dc or bias

calculations from small-signal calculations. That is, once a stable dc operating point has been established and all dc quantities calculated, we may then perform signal analysis ignoring dc quantities.

ಹಿಂದಿನ ವಿಶೇ್ಣಪಣೆಯಿಂದ, ಸಣ್ಣ-ಸಂಕೇತ ಅಂದಾಜು ಅಡಿಯಲ್ಲಿ, ಡಿಸಿ ಪ್ರಮಾಣಗಳ ಮೇಲೆ ಸಿಗ್ನಲ್ ಪ್ರಮಾಣಗಳನ್ನು ಸೂಪರ್ಇಂಫೋಸ್ ಮಾಡಲಾಗುತ್ತದೆ ಎಂದು ನಾವು ನೋಡುತ್ಕೆ ವೆ. ಉದಾಹರಣೆಗೆ, ಒಟ್ಟು ಡೈ್ರನ್ ಕರೆಂಟ್ ಐಡಿಯು ಡಿಸಿ ಕರೆಂಟ್ ಐಡಿ ಜೊತೆಗೆ ಸಿಗ್ನಲ್ ಕರೆಂಟ್ ಐಡಿ, ಒಟ್ಟು ಡೈ್ರನ್ ವೋಲ್ಟೇಜ್ ವಿಡಿಎಸ್ ಮತ್ತು ವಿಡಿಎಸ್ + ವಿ, ಮತ್ತು ಹೀಗೆ. ಸಣ್ಣ-ಸಂಕೇತ ಲೆಕ್ಕಾಚಾರಗಳಿಂದ ಡಿಸಿ ಅಥವಾ ಪಕ್ಷಪಾತ ಲೆಕ್ಕಾಚಾರಗಳನ್ನು ಬೇರ್ಪಡಿಸುವ ಮೂಲಕ ವಿಶೇ\_ಪಣೆ ಮತು ವಿನ್ಯಾಸವನ್ನು ಬಹಳವಾಗಿ ಸರಳಗೊಳಿಸಬಹುದು ಎಂದು ಅನುಸರಿಸುತ್ತದೆ. ಅಂದರೆ, ಸ್ಥಿರ ಡಿಸಿ ಆಪರೇಟಿಂಗ್ ಪಾಯಿಂಟ್ ಅನ್ನು ಸ್ಥಾಪಿಸಿದ ನಂತರ ಮತ್ತು ಎಲ್ಲಾ ಡಿಸಿ ಪ್ರಮಾಣಗಳನ್ನು ಲೆಕ್ಕ ಹಾಕಿದ ಪ್ರಮಾಣಗಳನ್ನು ನಿರ್ಲಕ್ಷಿಸಿ ನಾವು ಸಿಗ್ನಲ್ ವಿಶ್ಲೇಷಣೆಯನ್ನು ನಂತರ, ಮಾಡಬಹುದು.

Fig.1(m): Total instantaneous voltages v<sub>GS</sub> and v<sub>DS</sub>

# 1.44 Small Signal Equivalent Circuit Models:

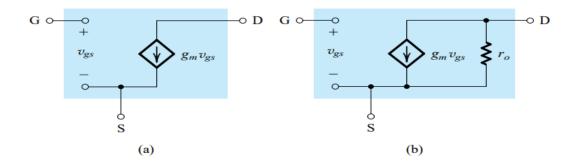

From a signal point of view, the FET behaves as a voltage-controlled current source. It accepts a signal  $v_{gs}$  between gate and source and provides a current  $g_m$   $v_{gs}$  at the drain terminal. The input resistance of this controlled source is very high—ideally, infinite. The output resistance—that is, the resistance looking into the drain—also is high, and we have assumed it to be infinite thus far. Putting all of this together, we arrive at the circuit in Fig. 1(n), which represents the small-signal operation of the MOSFET and is thus a small-signal model or a small-signal equivalent circuit. In the analysis of a MOSFET amplifier circuit, the transistor can be replaced by the equivalent circuit model shown in Fig. 1.n(a). The rest of the circuit remains unchanged except that ideal constant de voltage sources are replaced by short circuits. This is a result of the fact that the voltage across an ideal constant de voltage source does not change, and thus there will always be a zero voltage signal across a constant de voltage source. A dual statement applies for constant de current sources; namely, the signal current of an ideal constant de current source will always be zero, and thus an ideal constant de current source can be replaced by an open circuit in the small-signal equivalent circuit of the amplifier.

ಸಿಗ್ನಲ್ ದೃಷ್ಟಿಕೋನದಿಂದ, ಎಫ್ಇಟಿ ವೋಲ್ಕ್ಷೇಪ್ ನಿಯಂತ್ರಿತ ಪ್ರಸ್ತುತ ಮೂಲವಾಗಿ ವರ್ತಿಸುತ್ತದೆ. ಇದು ಗೇಟ್ ಮತ್ತು ಮೂಲದ ನಡುವೆ ಸಿಗ್ನಲ್ ವಿಜಿಗಳನ್ನು ಸ್ಟೀಕರಿಸುತ್ತದೆ ಮತ್ತು ಡೈ್ರನ್ ಟರ್ಮಿನಲ್ನಲ್ಲಿ ಪ್ರಸ್ತುತ ಗ್ರಾಂ ವಿಜಿಗಳನ್ನು ಒದಗಿಸುತ್ತದೆ. ಈ ನಿಯಂತ್ರಿತ ಮೂಲದ ಇನ್ಫುಟ್ ಪ್ರತಿರೋಧವು ತುಂಬಾ ಹೆಚ್ಚು-ಆದರ್ಶವಾಗಿ, ಅನಂತವಾಗಿದೆ. output ಪ್ರತಿರೋಧ (resistance)-ಅಂದರೆ, ಡೈ್ರನ್ (drain)ನಲ್ಲಿ ನೋಡುತ್ತಿರುವ ಪ್ರತಿರೋಧ (resistance)ವು ಹೆಚ್ಚಾಗಿರುತ್ತದೆ, ಮತ್ತು ನಾವು ಅದನ್ನು ಇಲ್ಲಿಯವರೆಗೆ ಅನಂತ ಎಂದು ಊಹಿಸಿದೇ್ನವೆ. ಇವೆಲ್ಲವನ್ನೂ ಒಟ್ಟುಗೂಡಿಸಿ, ನಾವು ಚಿತ್ರ 1 (ಎನ್) ನಲ್ಲಿ ಸರ್ಕ್ಯೂಟ್ಗ ಆಗಮಿಸುತ್ತೆವೆ, ಇದು MOSfet ನ ಸಣ್ಣ-ಸಂಕೇತ ಕಾರ್ಯಾಚರಣೆಯನ್ನು ಪ್ರತಿನಿಧಿಸುತ್ತದೆ ಮತ್ತು ಇದರಿಂದಾಗಿ ಸಣ್ಣ-ಸಂಕೇತ ಮಾದರಿ ಅಥವಾ ಸಣ್ಣ-ಸಂಕೇತ ಸಮಾನ ಸರ್ಕ್ಯೂಟ್ ಆಗಿದೆ. ಎಂಒಎಸ್ಎಫ್ಇಟಿ ಆಂಪ್ಲಿಫ್ಯಯರ್ ಸರ್ಕ್ಯೂಟ್ನ ವಿಶ್ಲ್ಪ್ಪಪಣೆಯಲ್ಲಿ, ಟ್ರಾನ್ಸಿಸ್ಟರ್ ಅನ್ನು ಚಿತ್ರ 1.n (ಎ) ನಲ್ಲಿ ತೋರಿಸಿರುವ ಸಮಾನ ಸರ್ಕ್ಯೂಟ್ ಮಾದರಿಯಿಂದ ಬದಲಾಯಿಸಬಹುದು. ಆದರ್ಶ ಸ್ಥಿರ ಡಿಸಿ ವೋಲ್ಟೇಜ್ ಮೂಲಗಳನ್ನು ಶಾರ್ಟ್ ಸರ್ಕ್ಯೂಟ್ಗಳಿಂದ ಬದಲಾಯಿಸಲಾಗುತ್ತದೆ ಎಂಬುದನ್ನು ಹೊರತುಪಡಿಸಿ ಉಳಿದ ಸರ್ಕ್ಯೂಟ್ ಬದಲಾಗದೆ ಉಳಿಯುತ್ತದೆ. ಆದರ್ಶ ಸ್ಥಿರ ಡಿಸಿ ವೋಲ್ಬೇಜ್ ಮೂಲದಾದಂ್ಯತ ವೋಲ್ಬೇಜ್ ಬದಲಾಗದೆ ಉಳಿಯುತ್ತದೆ. ಆದರ್ಶ ಸ್ಥಿರ ಡಿಸಿ ಫೋಲ್ಬೇಜ್ ಮೂಲದಾದಂ್ಯತ ವೋಲ್ಬೇಜ್

ಬದಲಾಗುವುದಿಲ್ಲ ಎಂಬ ಅಂಶದ ಪರಿಣಾಮವಾಗಿದೆ, ಮತ್ತು ಇದರಿಂದಾಗಿ ಸ್ಥಿರ ಡಿಸಿ ವೋಲ್ಟೇಜ್ ಮೂಲದಾದಂ್ಯತ ಯಾವಾಗಲೂ ಶೂನ್ಯ ವೋಲ್ಟೇಜ್ ಸಿಗ್ನಲ್ ಇರುತ್ತದೆ. ಸ್ಥಿರ dc ಪ್ರಸ್ತುತ ಮೂಲಗಳಿಗೆ ಒಂದು ದಂ್ವದ್ವ ಹೇಳಿಕೆ ಅನ್ವಯಿಸುತ್ತದೆ; ಹೆಸರಿಗೆ ತಕಂ್ಕತೆ, ಆದರ್ಶ ಸ್ಥಿರ ಡಿಸಿ ಪ್ರಸ್ತುತ ಮೂಲದ ಸಿಗ್ನಲ್ ಪ್ರವಾಹ ಯಾವಾಗಲೂ ಶೂನ್ಯವಾಗಿರುತ್ತದೆ, ಮತ್ತು ಹೀಗೆ ಒಂದು ಆದರ್ಶ ಸ್ಥಿರ ಡಿಸಿ ಪ್ರಸ್ತುತ ಮೂಲವನ್ನು ಆಂಪ್ಲಿಫಯರ್ನ ಸಣ್ಣ-ಸಂಕೇತ ಸಮಾನ ಸರ್ಕ್ಯೂಟ್ನಲ್ಲಿ ತೆರೆದ ಸರ್ಕ್ಯೂಟ್ನಿಂದ ಬದಲಾಯಿಸಬಹುದು.

एक सिग्नल दृष्टिकोनातून, FET एक व्होल्टेज नियंत्रित वर्तमान स्रोत म्हणून वागतात. हे गेट आणि स्रोत दरम्यान एक सिग्नल vgs स्वीकारतो आणि ड्रेन टर्मिनलवर वर्तमान ग्रम्म vgs प्रदान करते. या नियंत्रित स्रोत इनपुट प्रतिकार फार उच्च आहे - आदर्श, अनंत. आउटपुट प्रतिकार - म्हणजे, नाले मध्ये पाहणे प्रतिकार - देखील उच्च आहे, आणि आम्ही आतापर्यंत असीम असल्याचे गृहित धरले आहे. हे सर्व एकत्र ठेवत, आम्ही Fig. 1 (n) मधील सर्किटवर पोहोचतो, जो MOSFET च्या लहान-सिग्नल ऑपरेशनचे प्रतिनिधित्व करतो आणि अशा प्रकारे एक लहान-सिग्नल मॉडेल किंवा लहान-सिग्नल समतुल्य सर्किट आहे. एक MOSFET ऑम्प्लिफायर सर्किटच्या विश्लेषणात, ट्रान्झिस्टरला फिगमध्ये दर्शविलेल्या समतुल्य सर्किट मॉडेलद्वारे बदलले जाऊ शकते. 1. एन (ए). तो आदर्श सतत डीसी व्होल्टेज स्रोत शॉर्ट सर्किट बदलले आहेत वगळता उर्वरित सर्किट अपरिवर्तित राहते. हे एक आदर्श सतत डीसी व्होल्टेज स्रोत ओलांडून व्होल्टेज बदलत नाही की एक परिणाम आहे, आणि अशा प्रकारे नेहमी सतत डीसी व्होल्टेज स्रोत ओलांडून खून्य व्होल्टेज सिग्नल असेल. एक दुहेरी विधान सतत डीसी वर्तमान स्रोत लागू होते; नावापुरतेच, एक आदर्श सतत डीसी वर्तमान स्रोत सिग्नल चालू नेहमी शून्य असेल, आणि अशा प्रकारे एक आदर्श सतत डीसी वर्तमान स्रोत सिग्नल चालू नेहमी शून्य असेल, आणि अशा प्रकारे एक आदर्श सतत डीसी वर्तमान स्रोत वर्धक च्या लहान-सिग्नल समतुल्य सर्किट मध्ये एक ओपन सर्किट बदलले जाऊ शकते ..

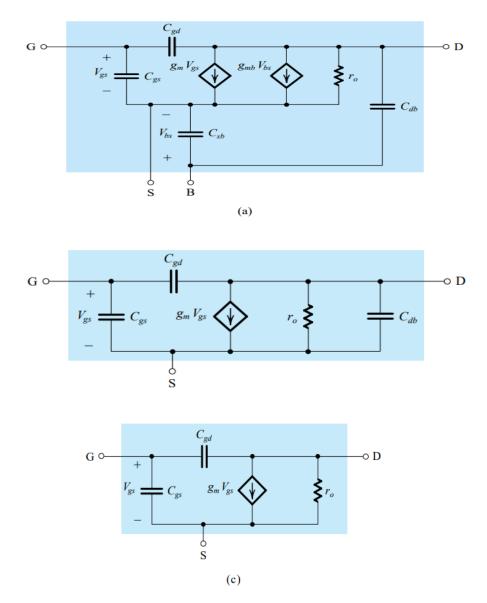

Fig:1(n): Small-signal models for the MOSFET: (a) neglecting the dependence of  $i_D$  on  $v_{DS}$  in saturation (the channel-length modulation effect); and (b) including the effect of channel-length modulation, modelled by output resistance.

The circuit resulting can then be used to perform any required signal analysis, such as calculating voltage gain.

The most serious shortcoming of the small-signal model of Fig. 1(n)(a) is that it assumes the drain current in saturation to be independent of the drain voltage. From our study of the MOSFET characteristics in saturation, we know that the drain current does in fact depend on  $v_{DS}$  in a linear manner. Such dependence was modelled by a finite resistance  $r_0$  between drain and source, whose value is given by

$$r_o = \frac{|V_A|}{I_D}$$

where is a MOSFET parameter that either is specified or can be measured. It should be recalled that for a given process technology,  $V_A$  is proportional to the MOSFET channel length. The current  $I_D$  is the value of the dc drain current without the channel-length modulation taken into account; that is

$$I_D = \frac{1}{2} k_n V_{OV}^2$$

Typically, ro is in the range of  $10 \text{ k}\Omega$  to  $1000 \text{ k}\Omega$ . It follows that the accuracy of the small signal model can be improved by including ro in parallel with the controlled source, as shown in Fig.1(n)(b). It is important to note that the small-signal model parameters gm and ro depend on the dc bias point of the MOSFET.

we find that replacing the MOSFET with the small-signal model of Fig. 1(n)(b) results in the voltage-gain expression

$$A_v = \frac{v_{ds}}{v_{gs}} = -g_m(R_D || r_o)$$

Thus, the finite output resistance ro results in a reduction in the magnitude of the voltage gain.

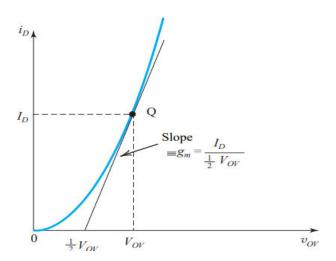

## 1.45 The Transconductance g<sub>m</sub>:

MOSFET transconductance equation described earlier can be rewritten with  $k_n$  = kn' (W / L) as follows:

$$g_m = k'_n(W/L)(V_{GS} - V_t) = k'_n(W/L)V_{OV}$$

This relationship indicates that  $g_m$  is proportional to the process transconductance parameter  $k_{n'} = \mu_n C_{OX}$  and to the W/L ratio of the MOS transistor; hence to obtain relatively large transconductance the device must be short and wide. We also observe that for a given device the transconductance is proportional to the overdrive voltage,  $V_{OV} = V_{GS} - V_t$ , the amount by which the bias voltage  $V_{GS}$  exceeds the threshold voltage  $V_t$ . Note, however, that increasing  $g_m$  by biasing the device at a larger  $V_{GS}$  has the disadvantage of reducing the allowable voltage signal swing at the drain.

Another useful expression for gm can be obtained by substituting for  $V_{OV}$  as  $\sqrt{[2I_D/kn'(W/L)]}$

$$g_m = \sqrt{2k'_n} \sqrt{W/L} \sqrt{I_D}$$

This expression shows two things:

- 1. For a given MOSFET, g<sub>m</sub> is proportional to the square root of the dc bias current.

- 2. At a given bias current,  $g_m$  is proportional to  $\sqrt{W/L}$

Yet another useful expression for gm of the MOSFET can be obtained by substituting for kn'(W / L) by  $2I_D$  /  $(V_{GS}-V_t)^2$

$$g_m = \frac{2I_D}{V_{GS} - V_t} = \frac{2I_D}{V_{OV}}$$

**Fig:1(n):** The slope of the tangent at the bias point Q intersects the  $v_{OV}$  axis at  $(1/2)V_{OV}$ .

Thus,

$$g_m = I_D / (1 / 2 V_{OV})$$

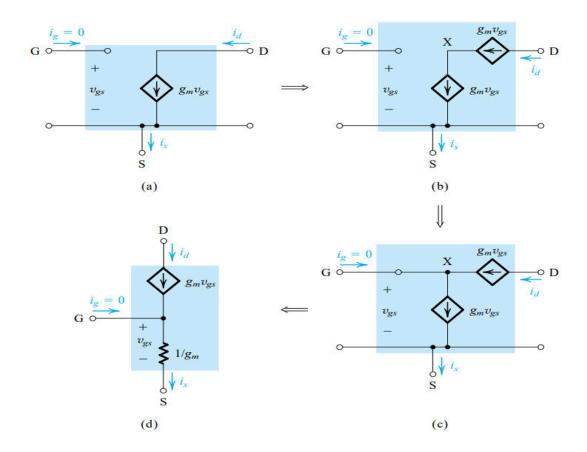

## 1.46 The T Equivalent Circuit model:

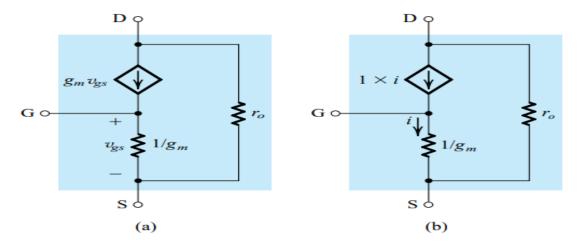

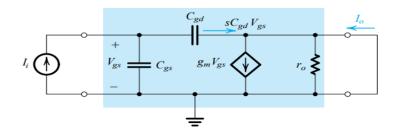

Through a simple circuit transformation, it is possible to develop an alternative equivalent-circuit model for the MOSFET. The development of such a model, known as the T model.

Figure 1(o):(a) shows the equivalent circuit studied above without  $r_0$ . Fig. 1(o)(b) we have added a second  $g_m$   $V_{gs}$  current source in series with the original controlled source. This addition obviously does not change the terminal currents and is thus allowed.

The newly created circuit node, labeled X, is joined to the gate terminal G in Fig. 1(o)(c). Observe that the gate current does not change—that is, it remains equal to zero—and thus this connection does not alter the terminal characteristics. We now note that we have a controlled current source  $g_m$   $v_{gs}$  connected across its control voltage  $v_{gs}$ . We can replace this controlled source by a resistance as long as this resistance draws an equal current as the source. Thus the value of resistance is  $V_{gs}$  /  $g_m$   $V_{gs}$  = 1 /  $g_m$ .

This replacement is shown in Fig. 1(o)(d), which depicts the alternative model. Observe that  $i_g$  is still zero,  $i_d = g_m V_{gs}$  and  $i_S = V_{gs} / (1 / g_m) = g_m V_{gs}$  which is same as shown in fig (a).

The model of Fig. 1(o)(d) shows that the resistance between gate and source looking into the source is This observation and the T model prove useful in many applications. Note that the resistance between gate and source, looking into the gate, is infinite.

In developing the T model we did not include  $r_0$ . If desired, this can be done by incorporating in the circuit of Fig. 1(o)(d) a resistance  $r_0$  between drain and source, as shown in Fig. 1(p)(a). An alternative representation of the T model, in which the voltage-controlled current source is replaced with a current-controlled current source, is shown in Fig. 1(p)(b).

**Fig:1(o):** Development of the T equivalent-circuit model for the MOSFET. For simplicity, r<sub>O</sub> has been omitted; however, it may be added between D and S in the T model of (d).

Fig:1(p):(a) The T model of the MOSFET augmented with the drain-to-source resistance ro. (b) An alternative representation of the T model.

**MOSFET Amplifier configuration**: Basic configurations, characterizing amplifiers, CS amplifier with and without source resistance RS, Source follower.

**MOSFET internal capacitances and High frequency model**: The gate capacitive effect, Junction capacitances, High frequency model.

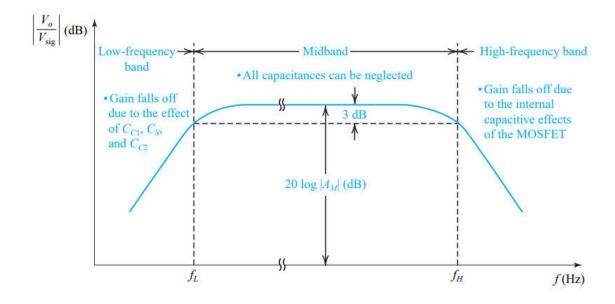

**Frequency response of the CS amplifier**: The three frequency bands, high frequency response, Low frequency response.

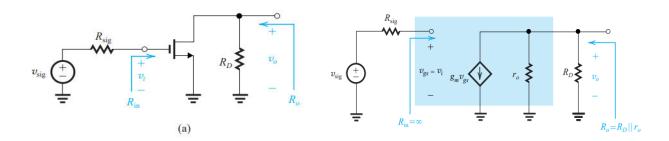

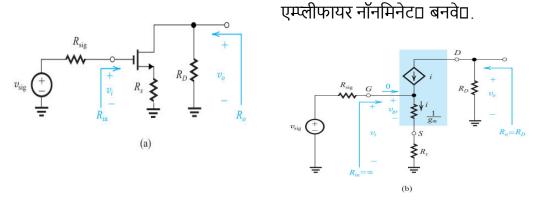

## **Basic MOSFET Amplifier configurations: The three Basic Configurations:**

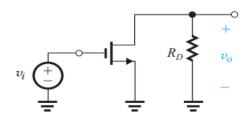

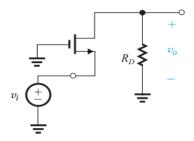

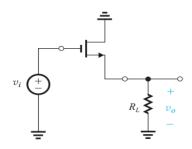

There are three basic configurations for connecting the MOSFET as an amplifier. Each of these configurations is obtained by connecting one of the three MOSFET terminals to ground, thus creating a two-port network with the grounded terminal being common to the input and output ports.

Figure 2.0 shows the resulting three configurations with the biasing arrangements omitted. In the circuit of Fig. 2(a) the source terminal is connected to ground, the input voltage signal is applied between the gate and ground, and the output voltage signal is taken between the drain and ground, across the resistance. This configuration, therefore, is called the grounded-source or common-source (CS) amplifier. The common-gate (CG) or grounded-gate amplifier is shown in Fig. 2(b). It is obtained by connecting the gate to ground, applying the input between the source and ground, and taking the output across the resistance connected between the drain and ground.

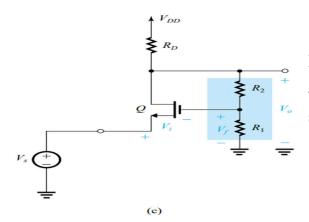

Finally, Fig.2(c) shows the common-drain (CD) or grounded-drain amplifier. It is obtained by connecting the drain terminal to ground, applying the input voltage signal between gate and ground, and taking the output voltage signal between the source and ground, across a load resistance. For reasons that will become apparent shortly, this configuration is more commonly called the source follower.

Fig:2(a):Common source(CS)

Fig:2(b): Common Gate (CG)

Fig: 2(c): Common Drain (CD)

ಎಂಒಎಸ್ಎಫ್ಇಟಿಯನ್ನು ಆಂಪ್ಲಿಫೈಯರ್ ಆಗಿ ಸಂಪರ್ಕಿಸಲು ಮೂರು ಮೂಲಭೂತ ಸಂರಚನೆಗಳಿವೆ. ಈ ಸಂರಚನೆಗಳಲ್ಲಿ ಪ್ರತಿಯೊಂದನ್ನು ಮೂರು ಎಂಒಎಸ್ಎಫ್ಇಟಿ ಟರ್ಮಿನಲ್ಗಳಲ್ಲಿ ಒಂದನ್ನು ನೆಲಕ್ಕೆ ಸಂಪರ್ಕಿಸುವ ಮೂಲಕ ಪಡೆಯಲಾಗುತ್ತದೆ, ಇದರಿಂದಾಗಿ ಎರಡು-ಪೋರ್ಟ್ ನೆಟ್ವರ್ಕ್ ಅನ್ನು ರಚಿಸುವುದರೊಂದಿಗೆ ನೆಲಸಮ ಟರ್ಮಿನಲ್ ಇನ್ಫುಟ್ ಮತ್ತು ಔಟ್ಫುಟ್ ಫೋರ್ಟ್ಮಳಿಗೆ ಸಾಮಾನ್ಯವಾಗಿದೆ.

ಚಿತ್ರ 2.0 ಪಕ್ಷಪಾತ ವ್ಯವಸ್ಥೆಗಳು ಕೈಬಿಡಲಾಯಿತು ಜೊತೆ ಪರಿಣಾಮವಾಗಿ ಮೂರು ಸಂರಚನೆಗಳನ್ನು ತೋರಿಸುತ್ತದೆ. ಚಿತ್ರ 2 (ಎ) ಯ ಸರ್ಕ್ಯೂಟ್ನಲ್ಲಿ ಮೂಲ ಟರ್ಮಿನಲ್ ನೆಲಕ್ಕೆ ಸಂಪರ್ಕ ಹೊಂದಿದೆ, ಇನ್ಫುಟ್ ಪೋಲ್ಟೆಜ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಗೇಟ್ ಮತ್ತು ನೆಲದ ನಡುವೆ ಅನ್ವಯಿಸಲಾಗುತ್ತದೆ, ಮತ್ತು ಔಟ್ಫುಟ್ ಪೋಲ್ಟೆಜ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಡೈ್ರನ್ ಮತ್ತು ನೆಲದ ನಡುವೆ, ಪ್ರತಿರೋಧದ ಉದ್ದಕ್ಕೂ ತೆಗೆದುಕೊಳ್ಳಲಾಗುತ್ತದೆ. ಆದ್ದರಿಂದ, ಈ ಸಂರಚನೆಯನ್ನು ಗ್ರೌಂಡೆಡ್-ಸೋರ್ಸ್ ಅಥವಾ ಕಾಮನ್-ಸೋರ್ಸ್ (ಸಿಎಸ್) ಆಂಪ್ಲಿಫೈಯರ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ. ಸಾಮಾನ್ಯ-ಗೇಟ್ (ಸಿಜಿ) ಅಥವಾ ಗ್ರೌಂಡೆಡ್-ಗೇಟ್ ಆಂಪ್ಲಿಫೈಯರ್ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ. ಸಾಮಾನ್ಯ-ಗೇಟ್ (ಸಿಜಿ) ಅಥವಾ ಗ್ರೌಂಡೆಡ್-ಗೇಟ್ ಆಂಪ್ಲಿಫುಯರ್ ಅನ್ನು ಚಿತ್ರ 2 (ಬಿ) ನಲ್ಲಿ ತೋರಿಸಲಾಗಿದೆ. ಗೇಟ್ ಅನ್ನು ನೆಲಕ್ಕೆ ಸಂಪರ್ಕಿಸುವ ಮೂಲಕ, ಮೂಲ ಮತ್ತು ನೆಲದ ನಡುವೆ ಇನ್ಫುಟ್ ಅನ್ನು ಅನ್ವಯಿಸುವ ಮೂಲಕ ಮತ್ತು ಡೈ್ರನ್ ಮತ್ತು ನೆಲದ ನಡುವೆ ಸಂಪರ್ಕ ಹೊಂದಿದ ಪ್ರತಿರೋಧದ ಉದ್ದಕ್ಕೂ ಔಟ್ಫುಟ್ ಅನ್ನು ತೆಗೆದುಕೊಳ್ಳುವ ಮೂಲಕ ಇದನ್ನು ಪಡೆಯಲಾಗುತ್ತದೆ.

ಅಂತಿಮವಾಗಿ, ಚಿತ್ರ 2 (ಸಿ) ಸಾಮಾನ್ಯ-ಡ್ಬ್ರೆನ್ (ಸಿಡಿ) ಅಥವಾ ಗ್ರೌಂಡೆಡ್-ಡ್ಬ್ರೆನ್ ಆಂಪ್ಲಿಫೈಯರ್ ಅನ್ನು ತೋರಿಸುತ್ತದೆ. ಡೈ್ರೆನ್ ಟರ್ಮಿನಲ್ ಅನ್ನು ನೆಲಕ್ಕೆ ಸಂಪರ್ಕಿಸುವ ಮೂಲಕ, ಗೇಟ್ ಮತ್ತು ನೆಲದ ನಡುವೆ ಇನ್ಪುಟ್ ಪೋಲ್ಟೆಜ್ ಸಿಗ್ನಲ್ ಅನ್ನು ಅನ್ವಯಿಸುವ ಮೂಲಕ ಮತ್ತು ಮೂಲ ಮತ್ತು ನೆಲದ ನಡುವೆ ಔಟ್ಪುಟ್ ಪೋಲ್ಟೆಜ್ ಸಿಗ್ನಲ್ ಅನ್ನು ತೆಗೆದುಕೊಳ್ಳುವ ಮೂಲಕ, ಒಂದು ಲೋಡ್ ಪ್ರತಿರೋಧದ ಉದ್ದಕ್ಕೂ ಇದನ್ನು

ಪಡೆಯಲಾಗುತ್ತದೆ. ಶೀಘ್ರದಲ್ಲೇ ಸ್ಪಪ್ಟವಾಗುವ ಕಾರಣಗಳಿಗಾಗಿ, ಈ ಸಂರಚನೆಯನ್ನು ಹೆಚ್ಚು ಸಾಮಾನ್ಯವಾಗಿ ಮೂಲ ಅನುಯಾಯಿ ಎಂದು ಕರೆಯಲಾಗುತ್ತದೆ.

एम्प्लिफायर म्हणून MOSFET कनेक्ट करण्यासाठी तीन मू□भूत कॉन्फिगरेशन आंोत. याती□ प्रत्येक संयोजना तीन MOSFET टर्मिनल्सपैकी एका टर्मिन□□ा ग्राउंडशी कनेक्ट करून प्राप्त कें□ी जाते, अशा प्रकारे दोन-पोर्ट नेटवर्क तयार कें□े जाते ज्यात ग्राउंड टर्मिन□ इनपुट आणि आउटपुट पोर्टसाठी सामान्य आंो.

आकृती 2.0 वगळ ☐ पक्षपाती व्यवस्था परिणामी तीन संरचना दाखवते. Fig. 2 (अ) च्या सर्किटमध्ये स्रोत टर्मिन ☐ जिमनीवर जोड ☐ अ ☐, इनपुट व्होल्टेज सिग्न ☐ गेट आणि ग्राउंड दरम्यान ☐ ागू के ☐ जाते आणि आउटपुट व्होल्टेज सिग्न ☐ आणि ग्राउंड दरम्यान, प्रतिकार ओ ☐ ंडून घेत ☐ जाते. म्हणूनच या कॉन्फिगरेशन ☐ ग्राउंडेड-सोर्स किंवा कॉमन-सोर्स (सीएस) एम्प्लीफायर असे म्हट ☐ जाते. सामान्य-गेट (सीजी) किंवा ग्राउंडेड-गेट वर्धक फिग 2 (बी) मध्ये दर्शवि ☐ आ ☐. तो जिमनीवर गेट कनेक्ट करून, स्रोत आणि ग्राउंड दरम्यान इनपुट अर्ज, आणि ना ☐ आणि ग्राउंड दरम्यान कनेक्ट प्रतिकार ओ ☐ ंडून आउटपुट घेऊन प्राप्त आ ☐.

शेवटी, Fig.2 (सी) कॉमन-ड्रेन (सीडी) किंवा ग्राउंडेड-ड्रेन वर्धक दर्शविते. तो जिमनीवर निचरा टर्मिन□ कनेक्ट करून, गेट आणि ग्राउंड दरम्यान इनपुट व्होल्टेज सिग्र□ अर्ज, आणि स्रोत आणि ग्राउंड दरम्यान आउटपुट व्होल्टेज सिग्र□ घेऊन, एक □ोड प्रतिकार ओ□ांडून प्राप्त आ□े. कारण □वकरच स्पष्ट □ोई□ की, □े कॉन्फिगरेशन अधिक सामान्यतः स्रोत अनुयायी म्हणतात.

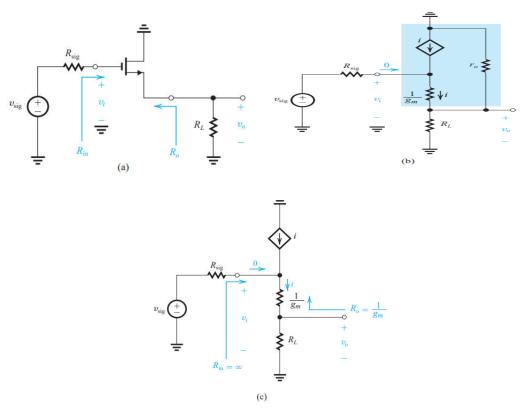

# 2.12 Characterizing Amplifiers:

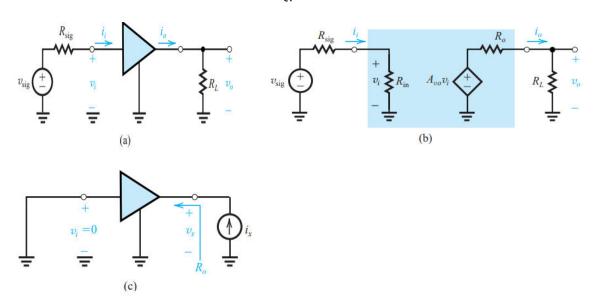

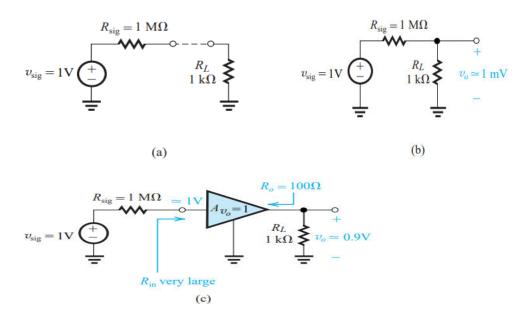

Figure 2.1(a) shows an amplifier fed with a signal source having an open-circuit voltage  $V_{sig}$  and an internal resistance  $R_{sig}$ . These can be the parameters of an actual signal source or, in a cascade amplifier, the Thévenin equivalent of the output circuit of another amplifier stage preceding the one under study. The amplifier is shown with a load resistance  $R_L$  connected to the output terminal. Here, can be an actual load resistance or the input resistance of a succeeding amplifier stage in a cascade amplifier.

ಚಿತ್ರ 2.1 (ಎ) ಓಪನ್-ಸರ್ಕ್ಯೂಟ್ ವೋಲ್ಟೇಜ್ ವಿಸಿಗ್ ಮತ್ತು ಆಂತರಿಕ ಪ್ರತಿರೋಧ Rsig ಅನ್ನು ಹೊಂದಿರುವ ಸಿಗ್ನಲ್ ಮೂಲದೊಂದಿಗೆ ಫೀಡ್ ಮಾಡಿದ ಆಂಪ್ಲಿಫಯರ್ ಅನ್ನು ತೋರಿಸುತ್ತದೆ. ಇವು ನಿಜವಾದ ಸಿಗ್ನಲ್ ಮೂಲದ ನಿಯತಾಂಕಗಳಾಗಿರಬಹುದು ಅಥವಾ ಕ್ಯಾಸ್ಕೇಡ್ ಆಂಪ್ಲಿಫೈಯರ್ನಲ್ಲಿ, ಅಧ್ಯಯನದ ಅಡಿಯಲ್ಲಿರುವ ಮತ್ತೊಂದು ಆಂಪ್ಲಿಫೈಯರ್

ಹಂತದ ಔಟ್ಫುಟ್ ಸರ್ಕ್ಯೂಟ್ನ ಥಿವೆನಿನ್ ಸಮಾನವಾಗಿರುತ್ತದೆ. ಆಂಪ್ಲಿಫಯರ್ ಔಟ್ಫುಟ್ ಟರ್ಮಿನಲ್ಗೆ ಸಂಪರ್ಕ ಹೊಂದಿದ ಲೋಡ್ ಪ್ರತಿರೋಧ ಆರ್ಎಲ್ನೊಂದಿಗೆ ತೋರಿಸಲಾಗಿದೆ. ಇಲ್ಲಿ, ನಿಜವಾದ ಲೋಡ್ ಪ್ರತಿರೋಧ ಅಥವಾ ಕ್ಯಾಸ್ಕೆಡ್ ಆಂಪ್ಲಿಫೈಯರ್ನಲ್ಲಿ ಯಶಸ್ವಿ ಆಂಪ್ಲಿಫೈಯರ್ ಹಂತದ ಇನ್ಫುಟ್ ಪ್ರತಿರೋಧವಾಗಿರಬಹುದು.

आकृती 2.1 (ए) एक ओपन-सर्किट व्होल्टेज Vsig आणि एक अंतर्गत प्रतिकार Rsig येत सिग्र□ स्रोत फीड एक प्रवर्धक दाखवते. ☐ प्रत्यक्ष सिग्र□ स्त्रोताचे मापदंड असू शकतात किंवा कॅस्केड एम्प्लीफायरमध्ये, अभ्यासाधीन अस्चेल्या दुसर्या एम्प्लीफायर स्टेजच्या आउटपुट सर्किटच्या थेव्हेनिन समतुल्य असू शकतात. वर्धक एक ☐ोड प्रतिकार आरए□ आउटपुट टर्मिन□ कनेक्ट स□ दर्शवि☐ आ☐. येथे, प्रत्यक्ष ☐ोड प्रतिकार किंवा कॅसकेड वर्धक मध्ये यशस्वी वर्धक स्टेज च्या इनपुट प्रतिकार असू शकते.

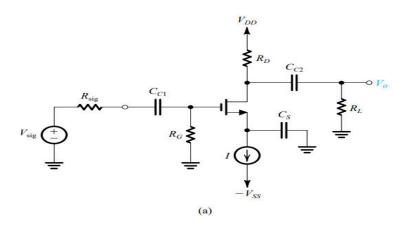

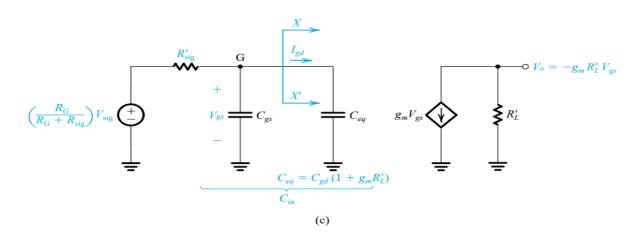

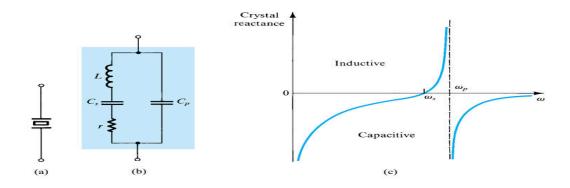

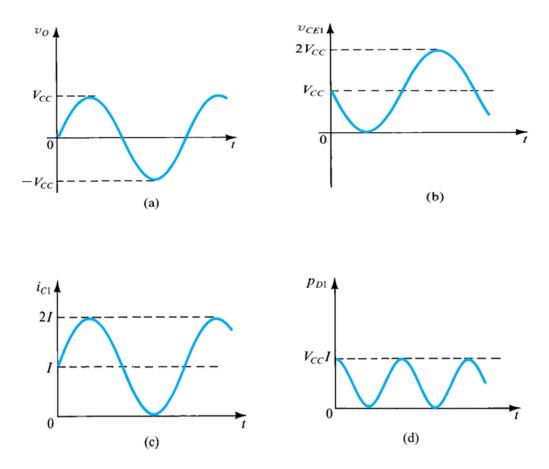

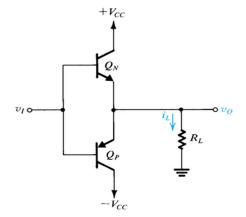

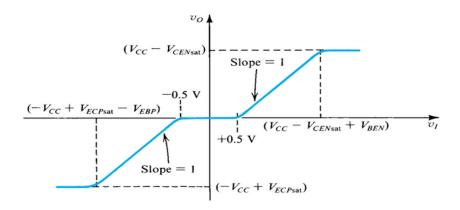

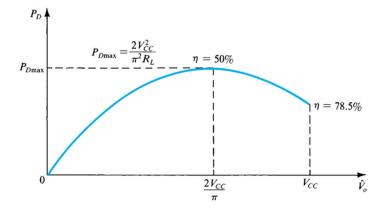

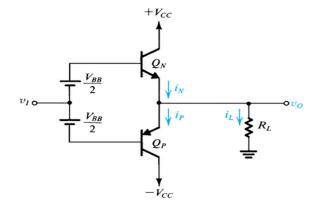

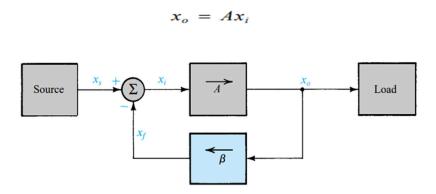

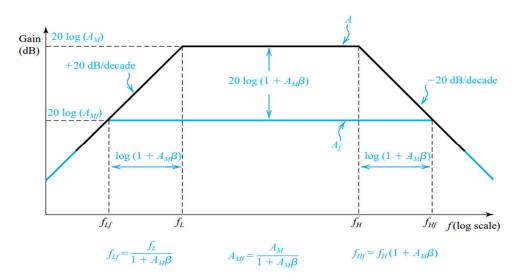

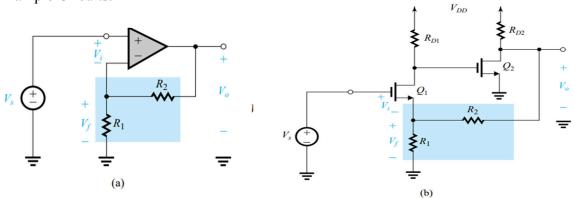

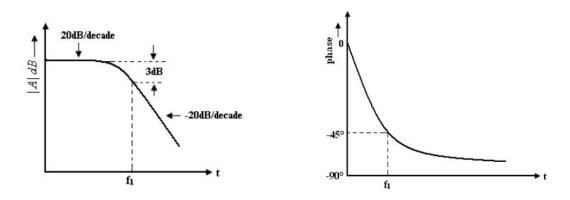

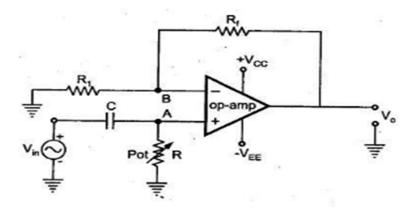

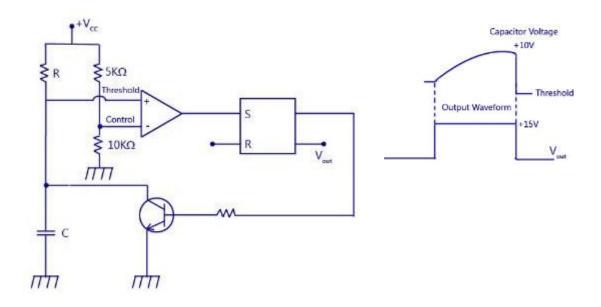

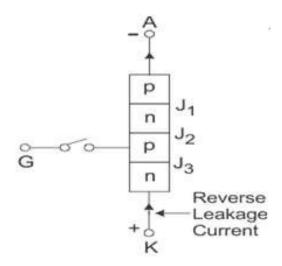

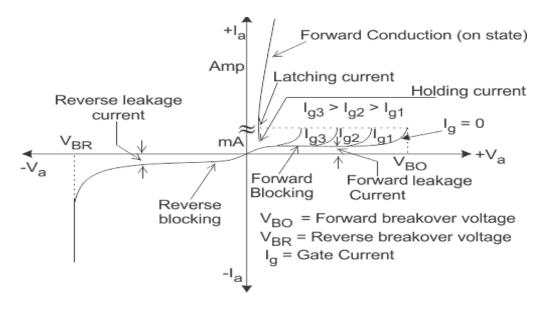

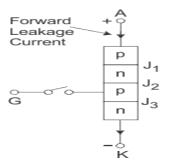

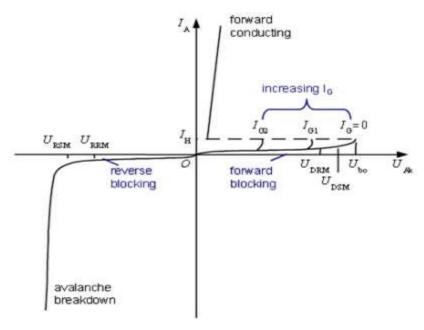

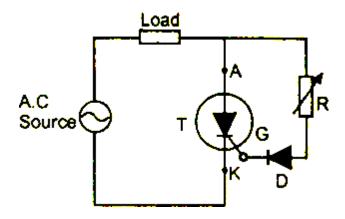

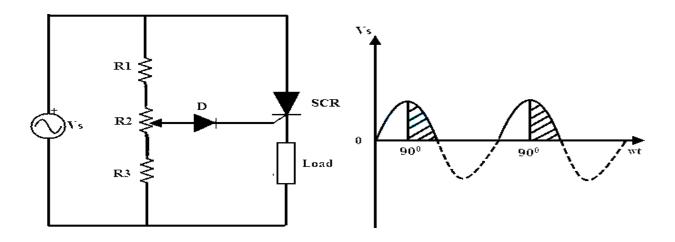

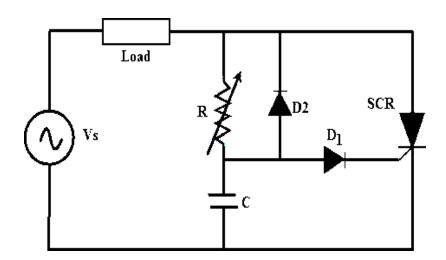

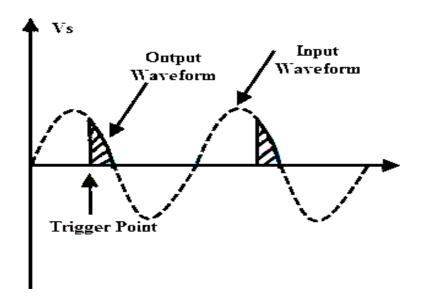

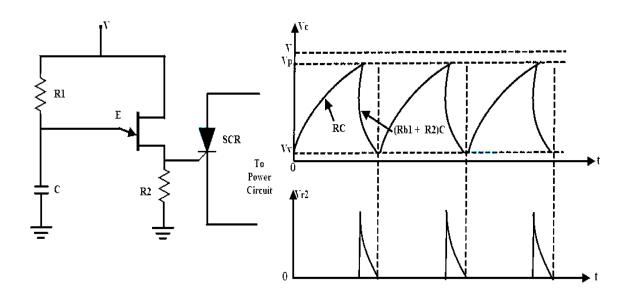

Fig: 2.1: Characterization of the amplifier as a functional block: (a) An amplifier fed with a voltage signal  $v_{sig}$  having a source resistance  $R_{sig}$ , and feeding a load resistance  $R_{L}$ ; (b) Equivalent-circuit representation of the circuit in (a); (c) Determining the amplifier output resistance  $R_{O}$ .